# الجمهورية الجزائرية الديمقراطية الشعبية وزارة التعليم العالي والبحث العلمي

RÉPUBLIQUE ALGÉRIENNE DÉMOCRATIQUE ET POPULAIRE

MINISTÈRE DE L'ENSEIGNEMENT SUPÉRIEUR ET DE LA RECHERCHE SCIENTIFIQUE

Ecole Supérieure en Génie Electrique et Energétique d'Oran Département du cycle préparatoire

المدرسة العليا في الهندسة الكهربانية و الطاقوية بوهران قسم التكوين التحضيري

Manuel de Cours, Travaux Dirigés et Travaux Pratiques

# Ingénierie 2

Ce manuel est destiné aux étudiants de 2<sup>éme</sup> année Des classes préparatoires en Génie Electrique et Energétique d'Oran

Réalisé par

**Dr Hendel Mounia**

MAITRE DE CONFERENCE "A" A L'ESG2E

Année Universitaire 2022/2023

# **Avant- propos**

Conformément au contenu du programme pédagogique de l'Ecole Supérieure en Génie Electrique et Energétique d'Oran, validé par arrêté ministériel, du ministère de l'enseignement supérieur et de la recherche scientifique, ce Manuel de cours, de Travaux Dirigés (TD) et de Travaux Pratiques (TP) s'adresse aux étudiants de la deuxième Année, module "Ingénierie 2". Ce support a pour principale objectif, la maitrise des notions fondamentaux des systèmes automatisés circuits logiques combinatoires et séquentiels, Grafcet et des Automates Programmables Industrielles (API), et ceux au tour de 6 chapitres, de 3 fiches de TD et une fiche de TP, des cours en ligne sont également disponibles et dont les liens sont en attachés à la fin de chaque chapitre :

- CHAPITRE 1 : LES SYSTEMES AUTOMATISES.

- CHAPITRE 2 : CIRCUITS COMBINATOIRES.

- CHAPITRE 3 : SYSTEMES LOGIQUES SEQUENTIELS.

- CHAPITRE 4 : COURS COMPTEURS/DECOMPTEURS.

- CHAPITRE 5 : LE GRAFCET.

- CHAPITRE 6: LES AUTOMATES PROGRAMMABLES INDUSTRIELS (API).

- Fiche TD 1 : Logique combinatoire et Logique Séquentielle.

- Fiche TD 2 : Les compteurs/Décompteurs synchrones/Asynchrone.

- Fiche TD 3 : GRAFCET.

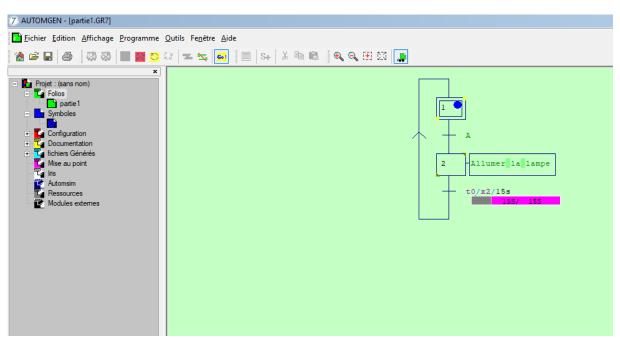

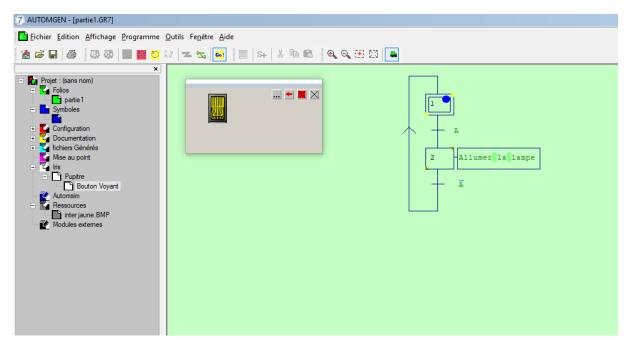

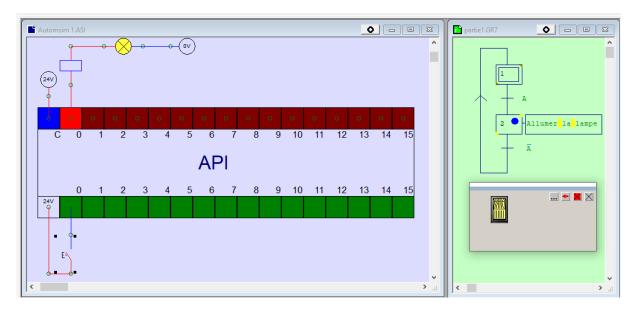

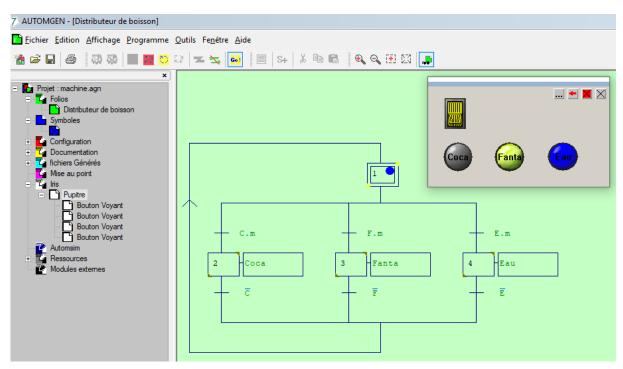

- TP 1 : Grafcet et API sous AUTOMGEN.

# **Avant- propos:**

Conformément au contenu du programme pédagogique de l'Ecole Supérieure en Génie Electrique et Energétique d'Oran, validé par arrêté ministériel, du ministère de l'enseignement supérieur et de la recherche scientifique, ce Manuel de cours, de Travaux Dirigés (TD) et de Travaux Pratiques (TP) s'adresse aux étudiants de la deuxième Année, module "Ingénierie 2". Ce support a pour principale objectif, la maîtrise des notions fondamentaux des systèmes automatisés circuits logiques combinatoires et séquentiels, Grafcet et des Automates Programmables Industrielles (API), et ceux au tour de 6 chapitres, de 3 fiches de TD et une fiche de TP, des cours en ligne sont également disponibles et dont les liens sont en attachés à la fin de chaque chapitre :

- CHAPITRE 1 : LES SYSTÈMES AUTOMATISES.

- CHAPITRE 2: CIRCUITS COMBINATOIRES.

- CHAPITRE 3 : LOGIQUES SÉQUENTIELS.

- CHAPITRE 4 : COURS COMPTEURS/DÉCOMPTEURS.

- CHAPITRE 5 : LE GRAFCET.

- CHAPITRE 6: LES AUTOMATES PROGRAMMABLES INDUSTRIELS (API).

- Fiche TD 1 : Logique combinatoire et Logique Séquentielle.

- Fiche TD 2 : Les compteurs/Décompteurs synchrones/Asynchrone.

- Fiche TD 3: GRAFCET.

- TP 1: Grafcet et API sous AUTOMGEN.

# **Table des matières**

| CHAPITRE 1 : LES SYSTÈMES AUTOMATISES                        |     |

|--------------------------------------------------------------|-----|

| 1.1 Définition d'système automatisé :                        | 3   |

| 1.2 La structure d'un système automatisé :                   | 1   |

| 1.2.1 Pupitre :                                              | 2   |

| 1.2.2 Partie Commande (PC)                                   | 2   |

| 1.2.3 Partie Opérative (PO)                                  | 2   |

| 1.2.4 Éléments d'interface :                                 | 2   |

| 1.3. Les modes de commande:                                  | 2   |

| 1.3.1 Mode de commande directe :                             | 2   |

| 1.3.2 Mode de commande avec compte rendu d'exécution :       | 2   |

| 1.4 Structure et fonctionnement d'une chaîne fonctionnelle : | 3   |

| 1.4.1 Chaîne d'information :                                 | 3   |

| 1.4.2 Chaîne d'énergie :                                     | 4   |

| CHAPITRE 2 : CIRCUITS COMBINATOIRES                          |     |

| 2.1 Définition :                                             |     |

| 2.2 Synthèse d'un circuit combinatoire                       | 7   |

| 2.3 Les circuits de transcodage :                            | 7   |

| a. Codeurs (Encodeur)                                        | 7   |

| b. Décodeur                                                  | 8   |

| c. Transcodeur Binaire/Gray:                                 | 10  |

| 2.2 Circuits d'aiguillage                                    | .11 |

| a. Le multiplexeur (sélecteur de données) :                  | 11  |

| b. Démultiplexeur :                                          | 12  |

| CHAPITRE 3 : SYSTÈMES LOGIQUES SÉQUENTIELS                   |     |

| 3.1 Définition                                               | 13  |

| 3.2 Circuits asynchrones et synchrones                       | 13  |

| a. Horloge :                                                 | .13 |

| b. Circuits asynchrones et synchrones                        | .13 |

| 3.3 Bascules (Bistables):                                    | 14  |

| 3.3.1 La bascule RS asynchrone                               | .14 |

| 3.3.2 La bascule RS synchrone                                | .15 |

| 3.3.3 Bascule J-K                                            | .16 |

| 3.3.4 Bascule D                                              | .16 |

| Fiche TD 1 : Logique combinatoire et Logique Séquentielle    | 18  |

| Solution   | n Fiche TD 1: Logique combinatoire et Logique Séquentielle                      | 23 |

|------------|---------------------------------------------------------------------------------|----|

| СНАРІ      | TRE 4 : COURS COMPTEURS/DECOMPTEURS                                             |    |

| 4.1        | Définitions :                                                                   | 34 |

| 4.2        | Les compteurs/décompteurs Asynchrones :                                         | 34 |

| 4.2        | .1 Compteurs asynchrones modulo 2 <sup>n</sup> (compteur binaire complet) :     | 34 |

| 4.2        | .2 Compteurs binaires asynchrones incomplets :                                  | 36 |

| 4.2        | .3 Décompteurs asynchrones modulo 2 <sup>n</sup> (décompteur binaire complet) : | 37 |

| 4.2        | .4 Décompteurs binaires asynchrones incomplets :                                | 38 |

| 4.2        | .5 Exercice 1 :Compteur/decompeur                                               | 40 |

| 4.2        | .6 Les avantages et limites des compteurs/décompteurs asynchrones :             | 40 |

| 4.3        | Synthèse d'un compteur/décompteur synchrone :                                   | 41 |

| 4.3        | .1 Table d'excitation d'une bascule :                                           | 42 |

| 4.3        | .2 Exercice 2 : synthétise d'un compteur synchrone                              | 45 |

| Fiche T    | D 2 : Les compteurs/Décompteurs synchrones/Asynchrone                           | 47 |

| Solution   | n Fiche TD 2 : Les compteurs/Décompteurs synchrones/Asynchrone                  | 48 |

| CHAPI      | TRE 5 : LE GRAFCET                                                              |    |

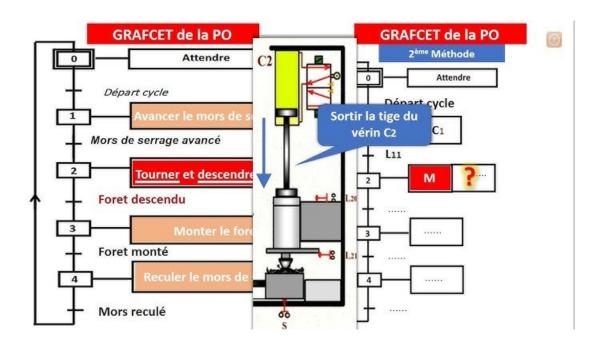

| 5.1        | C'est quoi le GRAFCET ?                                                         | 53 |

| 5.2        | Les éléments de base du GRAFCET :                                               | 53 |

| 5.2        | .1 Étape :                                                                      | 53 |

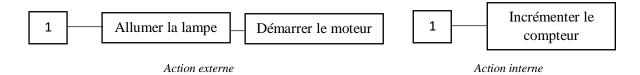

| 5.2        | .3 Action:                                                                      | 54 |

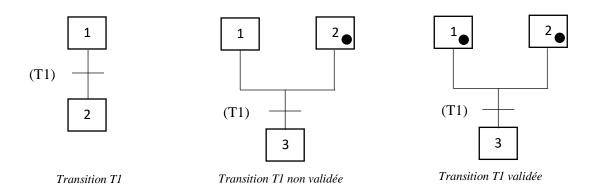

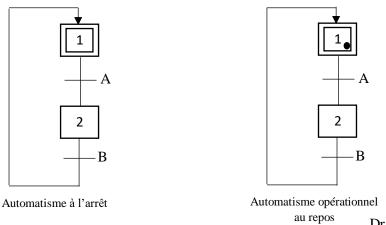

| 5.2        | .4 Transitions :                                                                | 54 |

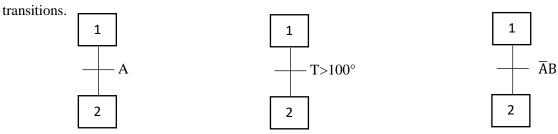

| 5.2        | .5 Réceptivités :                                                               | 55 |

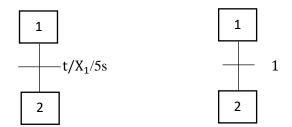

| 5.2        | .6 Liaisons orientées :                                                         | 55 |

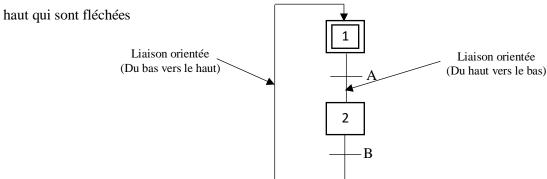

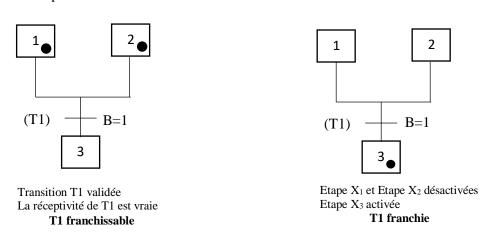

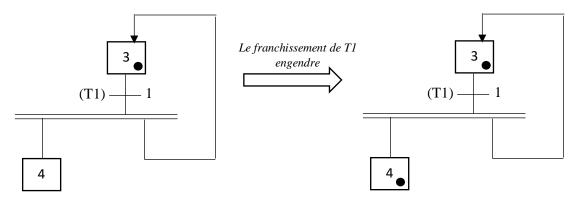

| 5.3        | Les règles d'évolutions du GRAFCET :                                            | 55 |

| <b>5.4</b> | Les séquences de base du GRAFCET :                                              | 57 |

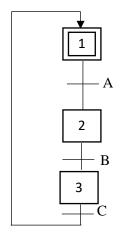

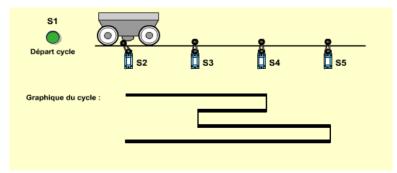

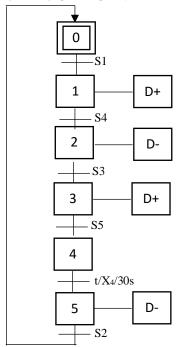

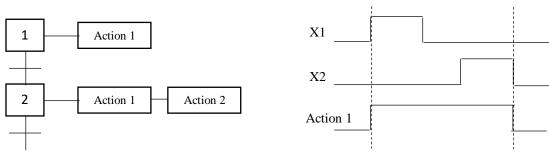

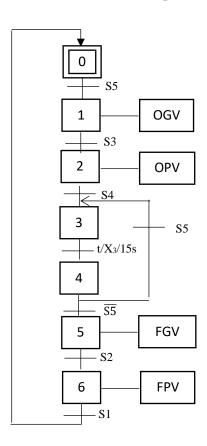

| 5.4        | .1 Grafcet à séquence unique :                                                  | 57 |

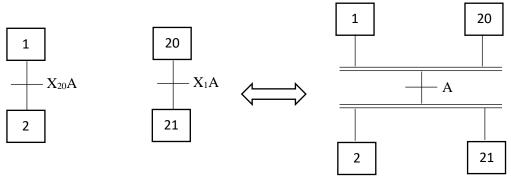

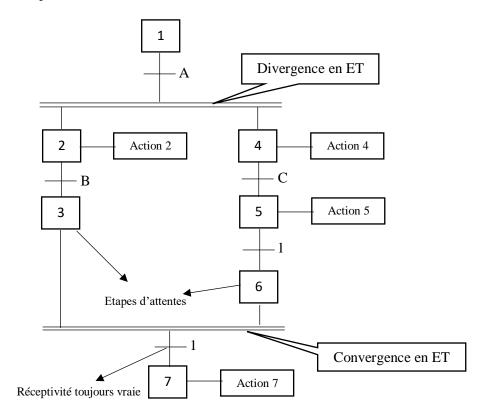

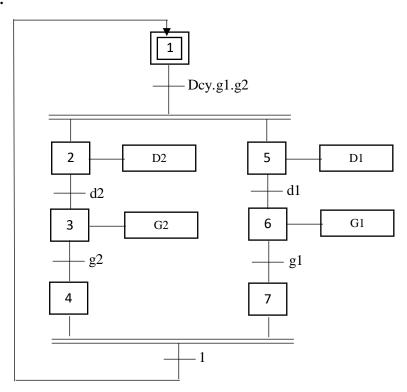

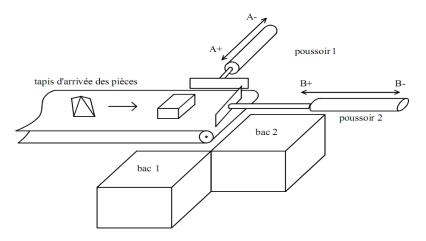

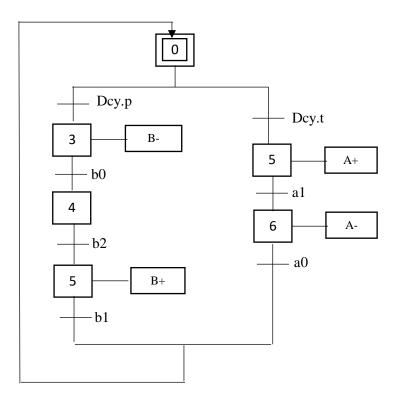

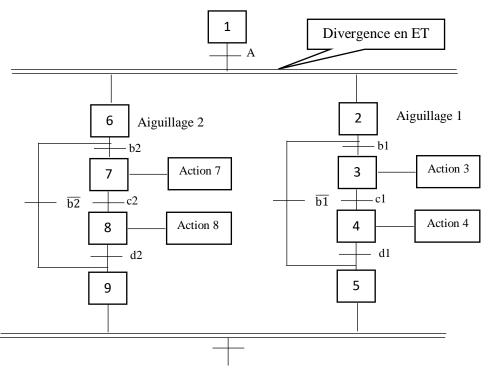

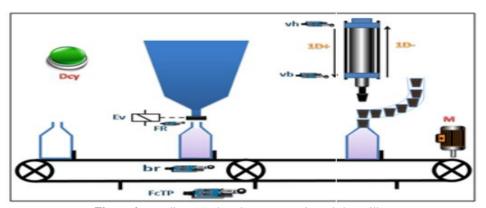

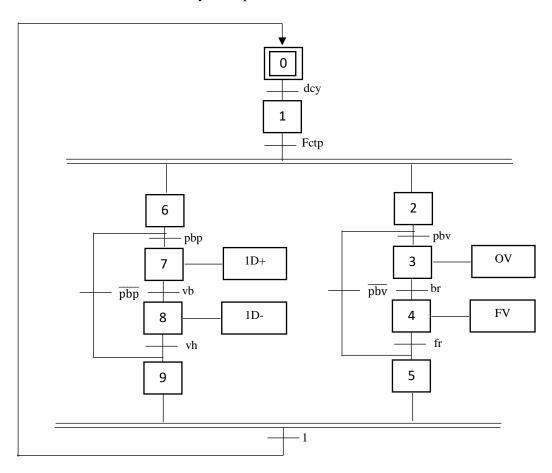

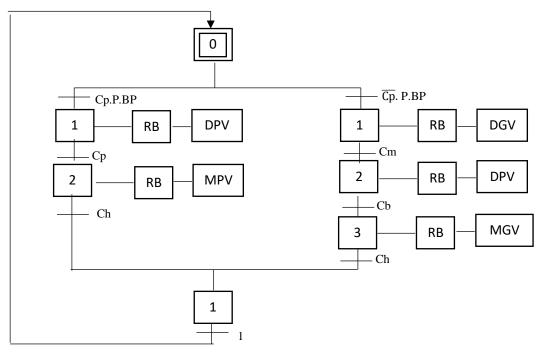

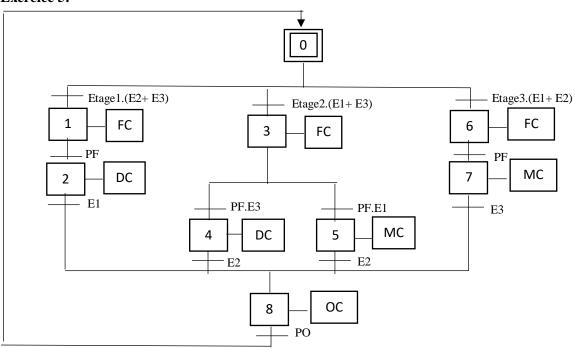

| 5.4        | .2 Grafcet à séquences simultanées (aiguillage en ET/ parallélisme structurel): | 59 |

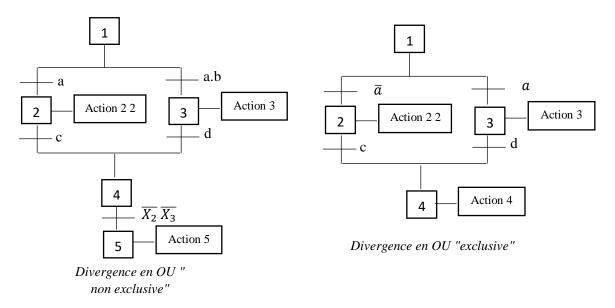

| 5.4        | .3 Grafcet avec choix de séquences (aiguillage en OU) :                         | 61 |

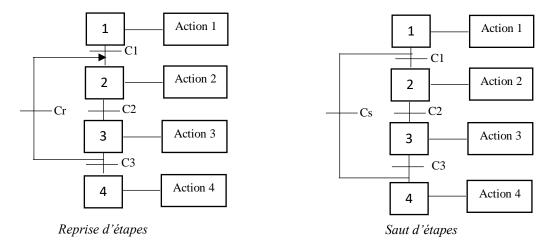

| 5.4        | .4 Grafcet à saut (et/ou) reprise de séquences :                                | 63 |

| 5.4        | .5 Aiguillage après activation simultanée des séquences :                       | 63 |

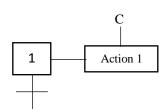

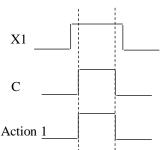

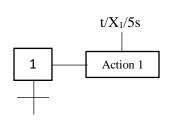

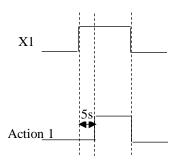

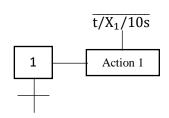

| 5.5        | La classification des actions d'un GRAFCET :                                    | 66 |

| 5.5        | .1 Action continue inconditionnelle :                                           | 66 |

| 5.5        | .2 Action continue conditionnelle :                                             | 67 |

| 5.5        | .3 Action continue retardée :                                                   | 67 |

| 5.5        | .4 Action continue à durée limitée :                                            | 67 |

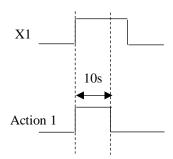

| 5.5        | .5 Action impulsionnelle :                                                      | 68 |

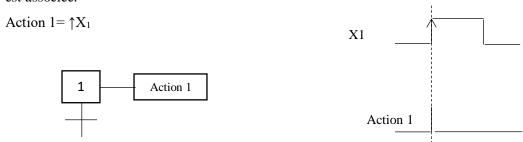

| 5.5        | .6 Action maintenu :                                                            | 68 |

| Fiche T  | TD 1: GRAFCET                                        | 69 |

|----------|------------------------------------------------------|----|

| Solution | n Fiche de TD 1: GRAFCET                             | 73 |

|          |                                                      |    |

| CHAPI    | TRE 6: LES AUTOMATES PROGRAMMABLES INDUSTRIELS (API) |    |

| 6.1      | Introduction :                                       | 78 |

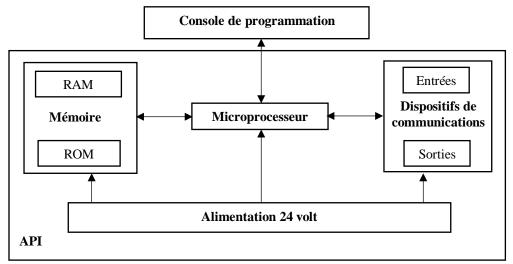

| 6.2      | Qu'est-ce qu'un API ?                                | 80 |

| 6.3      | Les constituants d'un API :                          | 80 |

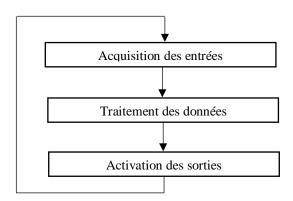

| 6.4      | Cycle de fonctionnement d'un API :                   | 81 |

| 6.5      | Critères de choix d'un API :                         | 82 |

| 6.6      | Langage de programmation d'un API :                  | 82 |

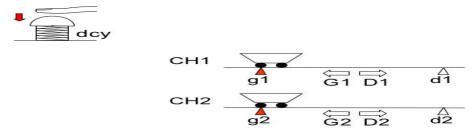

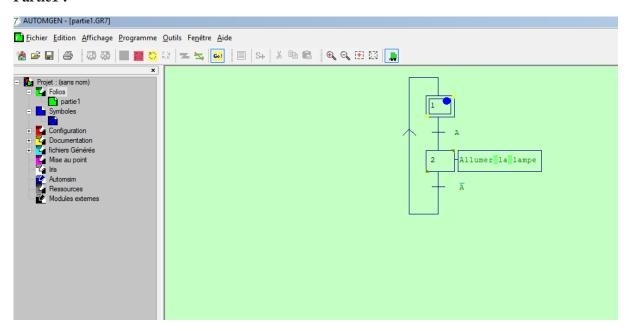

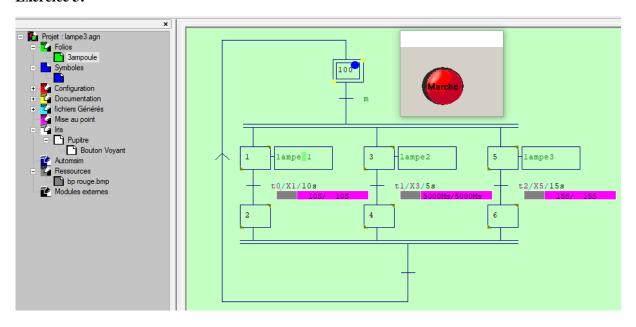

| TP: Gr   | afcet et API sous AUTOMGEN                           | 83 |

| Solution | n TP: Grafcet et API sous AUTOMGEN                   | 84 |

|          |                                                      |    |

# CHAPITRE 1: LES SYSTÈMES AUTOMATISES.

"L'apprentissage est une porte ouverte sur l'infini, chaque nouveau savoir étant une clé qui nous rapproche un peu plus de la compréhension du monde."

## **CHAPITRE 1: LES SYSTEMES AUTOMATISES**

Année: 2022-2023

Module : Ingénierie

### 1.1 Définition d'système automatisé :

C'est un système qui effectue le même cycle de travail pour lequel il a été programmé. C'est un système en mesure d'exécuter des tâches sans l'intervention de l'humain.

#### 1.2 La structure d'un système automatisé :

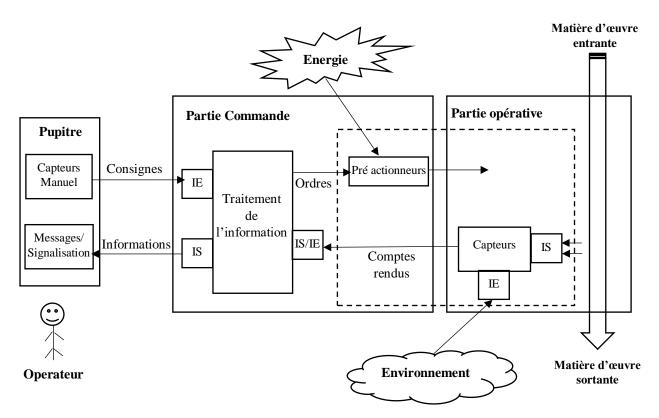

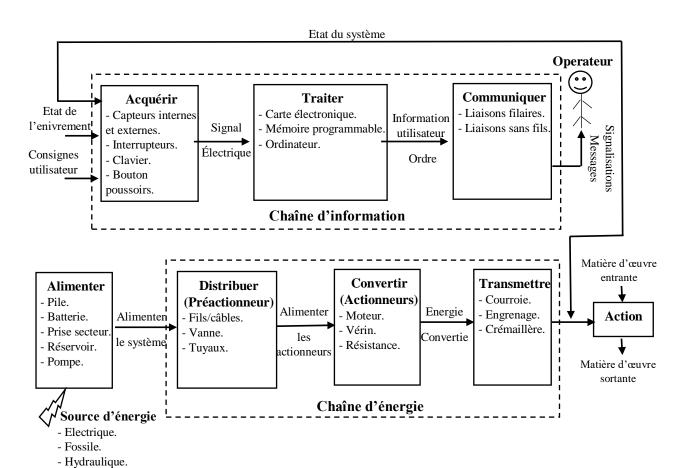

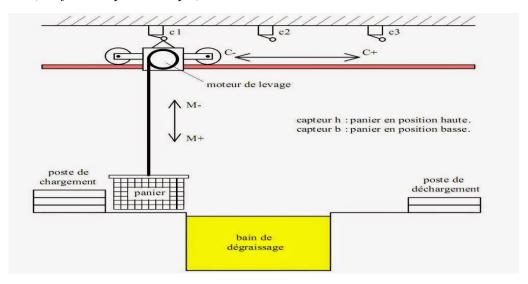

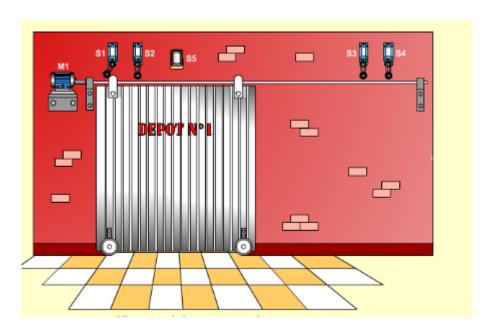

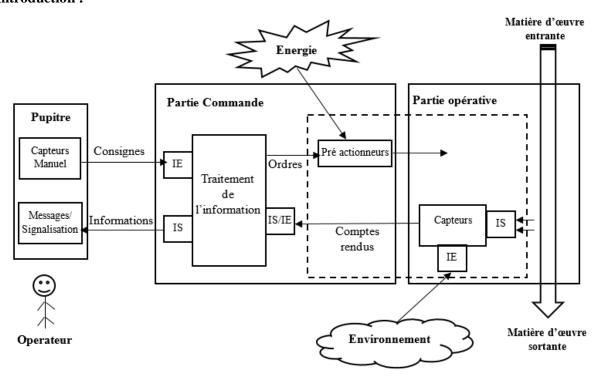

La structure d'un système automatisé est constituée principalement : d'un pupitre, d'une Partie Commande, d'une Partie Opérative, et deux éléments d'interface dénommé Pré-actionneurs et Capteurs (Figure 1.1).

Figure 1.1: Structure générale d'un système automatisé

- **1.2.1 Pupitre :** Assure le dialogue Homme/Partie-commande. L'utilisateur envois des consignes operateur (à partir du bouton Marche/Arrêt ou à partir d'un clavier), et reçoit des informations visuelles (à travers des signalisations et des messages...etc.).

- **1.2.2 Partie Commande** (**PC**): Elle représente l'ensemble des Moyens de traitement de l'information. La partie commande est considérée comme étant le "cerveau" qui gère le système automatisé. Elle adresse des ordres (consignes opératives) a la partie opérative, à partir :

- Du programme dont elle dispose.

- Des informations renvoies par les capteurs.

- Et les consignes données par l'utilisateur.

- **1.2.3 Partie Opérative (PO) :** Il s'agit de la partie qui effectue le travail dénommé "Machine", elle constitue l'ensemble des moyens techniques qui agissent sur la matière d'œuvre entrante pour avoir la matière d'œuvre sortante. De même qu'elle transmet à la partie commande les comptes rendu concernant l'état du système ou de l'environnement.

Année: 2022-2023

Module : Ingénierie

**1.2.4 Eléments d'interface :** Assure l'interaction entre la partie commande et la partie opérative. On distingue deux organes à savoir : les pré-actionneurs et les capteurs (plus de détail dans la section 4)

#### 1.3. Les modes de commandes:

On déduit de la section précédente qu'un échange d'informations est obligatoire entre la PC et la PO; Ces informations sont respectivement de type Ordres et Comptes rendus. En effet, la PO transfert à la PC des comptes rendus concernant l'état du système ou de l'environnement, et en se basant sur ces informations la PC envois des ordres a la PO.

Une fois les ordres (actions) établis par la PC, la PO effectue les actions demandées. On distingue donc, deux modes de commandes qui peuvent être utilisés par un système automatisé:

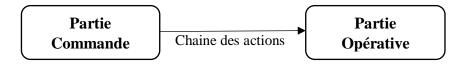

#### 1.3.1 Mode de commande directe :

Dénommée aussi système a chaine ouverte; la PC adresse des ordres a la PO, sans vérifier si les actions ont bien été réalisé.

Par exemple, les feux tri colores, le système ne vérifie pas si les voitures se sont bien arrêtées.

Figure 1.2: Mode de commande directe

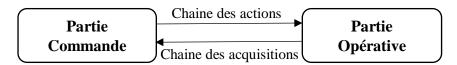

#### 1.3.2 Mode de commande avec compte rendu d'exécution :

Dénommé aussi système a chaine fermée, la partie commande du système vérifie que les actions demandées ont été bien réalisé par les PO. Ce type de systèmes sont considéré meilleur et plus fiable.

Par exemple, le passage à niveau, la barrière se lève à condition que le système est vérifier que le train est bien passé.

Année: 2022-2023

Module : Ingénierie

Figure 1.3: Mode de commande avec compte-rendu d'exécution

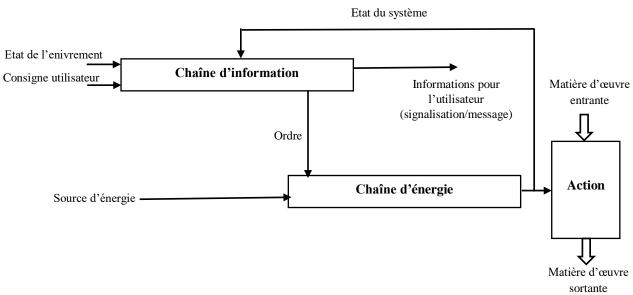

#### 1.4 Structure et fonctionnement d'une chaîne fonctionnelle :

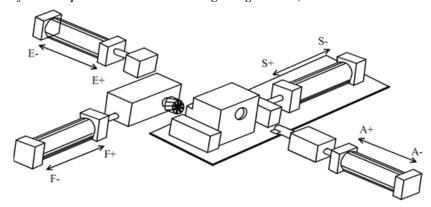

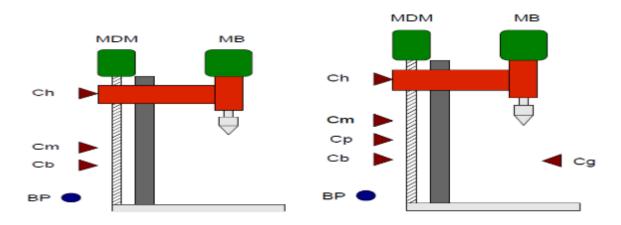

Tout système automatisé peut être constitue d'une ou de plusieurs chaînes fonctionnelles. Par exemple un système automatisé d'assemblage de petite voiture pour enfant (voir figure 1.4) est constitué de quatre chaînes fonctionnelles suivantes :

- Montage du châssis,

- Avance du plateau,

- Sertissage,

- Montage des roues.

Chaque chaîne fonctionnelle est subdivisée en une chaîne d'information et une chaîne d'énergie (Figure 1.4).

Figure 1.4: schéma simplifier d'une chaine fonctionnelle

#### 1.4.1 Chaîne d'information :

La chaîne d'information est constituée de trois blocs représentant chacun une fonction.

*a)* Fonction "Acquérir": elle va servir à recevoir les informations provenant de l'utilisateur par l'intermédiaire de capteurs manuels: boutons poussoirs, interrupteurs, claviers, télécommandes...etc.

De même, qu'elle va recevoir des informations du système ou de l'environnement extérieur via les capteurs interne est externe.

Année: 2022-2023

Module : Ingénierie

- b) Fonction "Traiter": C'est la partie intelligente du système automatisé. Elle va permettre de décider ce que le système doit faire, et ceux en fonction des informations reçu du système et de l'utilisateur.

- Dans cette partie on peut trouver des éléments tel des : cartes électroniques, automates programmables, Ordinateurs...etc.

- c) Fonction "Communiquer": la fonction va permettre d'une part d'informé le système de ce qui doit être fait par la suite (des ordres).

- Mais également, elle va communiquer des informations visuelles ou sonore sous forme: logique (lampe ou alarme), numérique (afficheur), ou analogique (compteur); afin de lui indiquer par exemple ce qui a étais fait.

Dans ce bloc on peut trouver des liaisons filaires (câbles, fils), ou des liaisons sans fils (wifi, radio, bleutooth).

**Remarque :** les capteurs sont des éléments embarqué dans les systèmes automatisés, ils permettent de transformer la variation d'une grandeur physique participant au fonctionnement de l'automatisme en un signal électrique.

#### 1.4.2 Chaîne d'énergie :

La chaîne d'énergie est constituée de quatre blocs représentant chacun une fonction bien déterminé.

a) Fonction alimenter: elle consiste à alimenter le système en énergie afin d'assurer l'action sur la matière d'œuvre.

La source d'énergie pour alimenter un système automatisé peut se présenter sous plusieurs natures: électrique, hydraulique, fossile...etc.

Ainsi le système d'alimentation doit être en adéquation avec le type d'énergie à distribuer, par exemple:

- Pour une énergie électrique, le système doit être menu d'une pile, une batterie, ou un secteur électrique.

- Pour une énergie fossile le système doit contenir un réservoir.

- Pour une énergie hydraulique, le système d'alimentation doit être de type pompe hydraulique.

Ecole Supérieure en Génie Electrique et Energétique d'Oran Département des Classes préparatoires

- b) Fonction distribuer : la fonction permet de distribuer l'énergie a la partie opérative, en fonction des ordres issue de la chaine d'information (c'est le rôle des pré-actionneur).

Dans ce module on peut trouver par exemple :

- Des fils ou des câbles si le système utilise de l'énergie électrique.

- Des vannes ou des tuyaux si le système utilise une énergie fossile ou hydraulique.

Année: 2022-2023

Module : Ingénierie

- c) Fonction convertir : elle va permettre de transformer l'énergie distribué en une autre forme d'énergie, utilisable par les effecteurs de la partie opérative (c'est le rôle des actionneurs). Un actionneur peut par exemple être:

- Un moteur qui va transformer une énergie électrique en une énergie de rotation.

- Un vérin qui va recevoir de l'énergie électrique ou hydraulique, et en sortie il donne une énergie mécanique de translation.

- Une résistance qui va transformer une énergie électrique en une énergie thermique.

- d) Fonctions transmettre et action : c'est deux fonctions sont en générale exécutées par des mécanismes, en effet, ces blocs sont constitués des pièces relier entre elles par des liaisons mécaniques.

- Le rôle de ces liaisons mécanismes est de transmettre la nouvelle énergie obtenue à partir des actionneurs au effecteurs afin d'obtenir l'action voulus. Parmi les types de liaisons mécaniques existantes, on peut citer:

- Les courroies et les engrenages, qui va nous permettre d'accentuer ou de diminuer la cadence d'un mouvement de rotation.

- Des crémaillères qui va nous permettre de transformer un mouvement de rotation en un mouvement de translation, etc.

Année: 2022-2023

Module : Ingénierie

# **Biobibliographie:**

- [1] "Systèmes automatisés : Principes et applications" par Jean-Pierre Desbiens.[2] "Introduction to Automation and Control Systems" par William S. Levine.

- [3] "Fundamentals of Automation and Robotics" par Hassan A. Karimi.

# **CHAPITRE 2: CIRCUITS COMBINATOIRES.**

""Le véritable apprentissage ne consiste pas seulement à emmagasiner des connaissances, mais à transformer chaque découverte en une opportunité d'évoluer"

## **CHAPITRE 2: CIRCUITS COMBINATOIRES**

Année: 2022-2023

Ingénierie

#### 2.1 Définition :

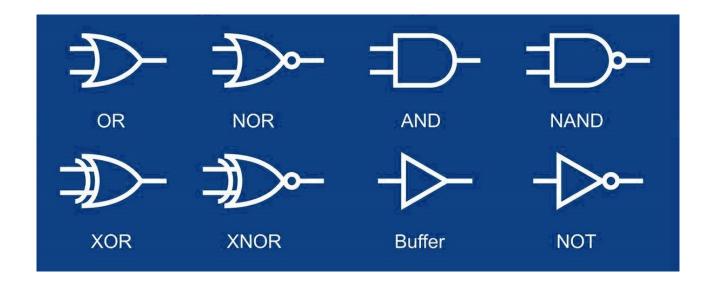

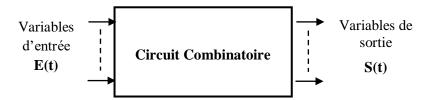

Un circuit combinatoire est un système composé d'un ensemble de portes logiques, et dont l'état de(s) sortie(s) à l'instant t est fonction exclusivement des variables présentées à son entrée au même instant: S(t) = F(E(t)). Ainsi l'application à l'entrée d'une même combinaison de variables conduira forcement a une sortie inchangée.

Fig. 2.1: schéma représentatif d'un circuit combinatoire.

#### 2.2 Synthèse d'un circuit combinatoire

La synthèse d'un circuit logique combinatoire consiste à proposer un logigramme répondant à un cahier des charges, les étapes de conception sont les suivantes :

- Identifier les entrées et les sorties (IN / OUT) du circuit.

- Construire la table (les tables) de vérité.

- Identifier chaque fonction à partir de la table de vérité.

- Simplifier chaque fonction.

- Dessiner le schéma du circuit.

## 2.3 Les circuits de transcodage :

Un circuit de transcodage est un circuit qui transforme une information présente en entrée sous une forme donnée : *code1*, en une information équivalente en sortie mais sous une autre forme : *code 2*Dans cette section nous allons faire la synthèse de trois circuits de transcodage couramment utilisés, à savoir :

- Les codeurs (encodeurs).

- Les décodeurs.

- Les transcodeurs Binaire/Gray.

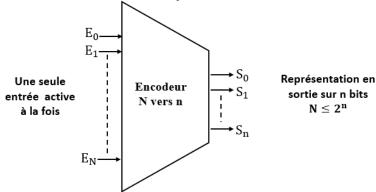

#### a. Codeurs (Encodeur)

Un codeur est un circuit à  $N = 2^n$  entrées et n sorties qui code en binaire le rang de la seule entrée activée. **Application pratique :** codeurs de clavier numérique.

Fig. 2.2: schéma représentatif d'un codeur.

Année: 2022-2023

Ingénierie

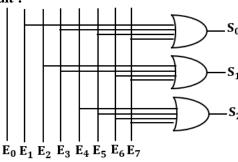

**Exemple 2.1:** Faire la synthèse d'un encodeur sur n=3 bits  $\rightarrow 2^3 = 8$  entrées et 3 sorties.

#### 1. Identification des entrées et des sorties (IN / OUT) du circuit :

- Entrées : encodeur sur n=3 bits  $\rightarrow$  N =  $2^3$  = 8 entrées :  $E_0$ ,  $E_1$ ,....,  $E_7$ .

- Sorties:  $n=3 \rightarrow 3$  sorties:  $S_0, S_1, S_2$ .

#### 2. Construction de la table (les tables) de vérité :

|   | Eo | $E_1$ | E <sub>2</sub> | $E_3$ | $E_4$ | E <sub>5</sub> | E <sub>6</sub> | E <sub>7</sub> | $S_0$ | $S_1$ | $S_2$ |

|---|----|-------|----------------|-------|-------|----------------|----------------|----------------|-------|-------|-------|

| 0 | 1  |       |                |       |       |                |                |                | 0     | 0     | 0     |

| 1 |    | 1     |                |       |       |                |                |                | 0     | 0     | 1     |

| 2 |    |       | 1              |       |       |                |                |                | 0     | 1     | 0     |

| 3 |    |       |                | 1     |       |                |                |                | 0     | 1     | 1     |

| 4 |    |       |                |       | 1     |                |                |                | 1     | 0     | 0     |

| 5 |    |       |                |       |       | 1              |                |                | 1     | 0     | 1     |

| 6 |    |       |                |       |       |                | 1              |                | 1     | 1     | 0     |

| 7 |    |       |                |       |       |                |                | 1              | 1     | 1     | 1     |

#### 3. Identifier chaque fonction à partir de la table de vérité et 4. simplifier chaque fonction :

$$S_2 = E_4 + E_5 + E_6 + E_7.$$

$$S_1 = E_2 + E_3 + E_6 + E_7.$$

$$S_0 = E_1 + E_3 + E_5 + E_7.$$

#### 5. Dessiner le schéma du circuit :

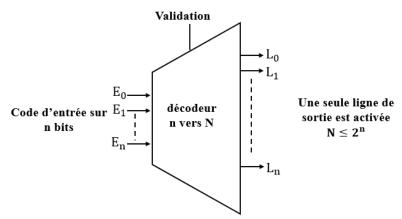

#### b. Décodeur

Joue le rôle inverse d'un codeur, il est constitué de :

- **n** Entrées de données : Code sur n bits

- 2<sup>n</sup> Sorties (lignes)

- A chaque code en entrée, une ligne de sortie est sélectionnée

Application pratique : Adressage d'une mémoire, Génération de fonctions

Année: 2022-2023

Ingénierie

Fig. 2.3: schéma représentatif d'un décodeur.

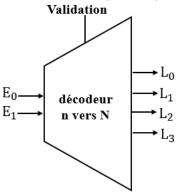

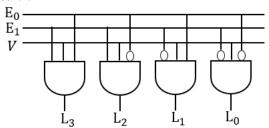

Exemple 2.2 : Faire la synthèse d'un décodeur 4 voies (2 vers 4).

#### 1. Identification des entrées et des sorties (IN / OUT) du circuit :

Entrées : 2 entrées :  $E_0$ ,  $E_1$ .

- Sorties: 4 sorties  $N = 2^n = 2^2 = L_0, L_1, L_2, L_3$ .

#### 2. Construction de la table (les tables) de vérité :

|       |    | V     | =0    |       |       |

|-------|----|-------|-------|-------|-------|

| $E_1$ | Eo | $L_3$ | $L_2$ | $L_1$ | $L_0$ |

| 0     | 0  | 0     | 0     | 0     | 0     |

| 0     | 1  | 0     | 0     | 0     | 0     |

| 1     | 0  | 0     | 0     | 0     | 0     |

| 1     | 1  | 0     | 0     | 0     | 0     |

|       |    | V     | =1    |       |       |

|-------|----|-------|-------|-------|-------|

| $E_1$ | Eo | $L_3$ | $L_2$ | $L_1$ | $L_0$ |

| 0     | 0  | 0     | 0     | 0     | 1     |

| 0     | 1  | 0     | 0     | 1     | 0     |

| 1     | 0  | 0     | 1     | 0     | 0     |

| 1     | 1  | 1     | 0     | 0     | 0     |

#### 3. Identifier chaque fonction à partir de la table de vérité et 4. simplifier chaque fonction :

$$L_0 = \overline{E}_1.\overline{E}_0.\overline{V}$$

,  $L_1 = \overline{E}_1.\overline{E}_0.\overline{V}$  ,  $L_2 = \overline{E}_1.\overline{E}_0.\overline{V}$  ,  $L_3 = \overline{E}_1.\overline{E}_0.\overline{V}$

#### 5. Dessiner le schéma du circuit :

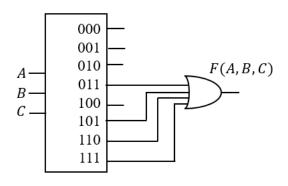

**Exemple 2.3 :** Générer la fonction logique ci-dessous à l'aide d'un décodeur 3 vers 8  $F(A, B, C) = CB\bar{A} + C\bar{B}A + \bar{C}BA + CBA$

Ecole Supérieure en Génie Electrique et Energétique d'Oran Département des Classes préparatoires

| A | В | С | F(A,B,C) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 0        |

| 0 | 1 | 0 | 0        |

| 0 | 1 | 1 | 1        |

| 1 | 0 | 0 | 0        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | 1        |

| 1 | 1 | 1 | 1        |

Année: 2022-2023

Ingénierie

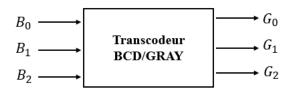

#### c. Transcodeur Binaire/Gray:

C'est un circuit combinatoire qui permet de renvoyer en sortie en langage Gray (sur n bits), le même chiffre présenté en entrée en code binaire (sur n bits).

Exemple 4 : Faire la synthèse d'un transcodeur binaire / Gray (3bits)

## 1. Identification des entrées et des sorties (IN / OUT) du circuit :

-  $Entrées: 3 entrées: B_0, B_1, B_2.$

- Sorties:  $G_0$ ,  $G_1$ ,  $G_2$

#### 2. Construction de la table (les tables) de vérité :

|   | Entr  | ée bir | naire | Sort  | tie G1 | ay    |

|---|-------|--------|-------|-------|--------|-------|

|   | $B_2$ | $B_1$  | $B_0$ | $G_2$ | $G_1$  | $G_0$ |

| 0 | 0     | 0      | 0     | 0     | 0      | 0     |

| 1 | 0     | 0      | 1     | 0     | 0      | 1     |

| 2 | 0     | 1      | 0     | 0     | 1      | 1     |

| 3 | 0     | 1      | 1     | 0     | 1      | 0     |

| 4 | 1     | 0      | 0     | 1     | 1      | 0     |

| 5 | 1     | 0      | 1     | 1     | 1      | 1     |

| 6 | 1     | 1      | 0     | 1     | 0      | 1     |

| 7 | 1     | 1      | 1     | 1     | 0      | 0     |

# 3. Identifier chaque fonction à partir de la table de vérité :

$$\mathsf{G}_2 = \mathsf{B}_2\overline{\mathsf{B}_1}\ \overline{\mathsf{B}_0} + \mathsf{B}_2\overline{\mathsf{B}_1}\mathsf{B}_0 + \mathsf{B}_2\mathsf{B}_1\overline{\mathsf{B}_0} + \mathsf{B}_2\mathsf{B}_1\mathsf{B}_0.$$

$$G_1{=}\overline{B_2}B_1\overline{B_0}+\overline{B_2}B_1B_0+B_2\overline{B_1}\;\overline{B_0}\;{+}B_2\overline{B_1}B_0\;.$$

$$\mathsf{G}_0 = \overline{\mathsf{B}_2} \, \overline{\mathsf{B}_1} \mathsf{B}_0 + \overline{\mathsf{B}_2} \mathsf{B}_1 \overline{\mathsf{B}_0} + \mathsf{B}_2 \overline{\mathsf{B}_1} \mathsf{B}_0 + \mathsf{B}_2 \mathsf{B}_1 \overline{\mathsf{B}_0}.$$

## 4. simplifier chaque fonction:

| $B_0$    | 0 | 1 |

|----------|---|---|

| $B_2B_1$ |   |   |

| 00       | 0 | 0 |

| 01       | 0 | 0 |

| 11       | 1 | 1 |

| 10       | 1 | 1 |

$$G_2 = B_2$$

| $B_2B_1$ |   | 1 |

|----------|---|---|

| 00       | 0 | 0 |

| 01       | 1 | 1 |

| 11       | 0 | 0 |

| 10       | 1 | 1 |

$\searrow R_{\circ}$

0 1

$$G_2 = B_2$$

$G_1 = B_2\overline{B_1} + \overline{B_2}B_1 = B_2 \oplus B_1$

$$B_1\overline{B_0}$$

+

Année: 2022-2023

Ingénierie

$\overline{B_1}B_0=B_1 \oplus B_0$

#### 5. Dessiner le schéma du circuit :

#### 2.2 Circuits d'aiguillage

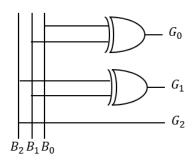

#### a. Le multiplexeur (sélecteur de données) :

Le multiplexeur est un circuit combinatoire Sélecteur qui possède  $2^n$  entrées d'information, n entrées de commande (Adresse), et une seule sortie. Son rôle consiste à sélectionner, à l'aide de signaux de commande, une des entrées et à l'envoyer à la sortie

**Exemple 5 :** Multiplexeur à N=2 entrées de commande

$E_2$  $E_2^n$  $A_{n-1} ... A_1 A_0$

Application pratique: Les multiplexeurs ont de nombreuses applications. Ils peuvent par exemple être utilisés comme :

- Sélecteur de données.

- Convertisseur parallèle-série. Le multiplexeur reçoit en parallèle des données qu'il peut transmettre l'une après l'autre sur sa sortie.

- Générateur de fonctions logiques. En fait un multiplexeur à n entrées d'adresses (et donc  $2^n$  entrées de données) peut réaliser toutes les fonctions logiques combinatoires de n + 1 variables.

**Exemple 6 :** réalisation de la fonction  $F = x y \overline{z} + \overline{x} \overline{y} z + y z$  avec un multiplexeur à 2 entrées d'adresse.

Ecole Supérieure en Génie Electrique et Energétique d'Oran Département des Classes préparatoires

On connecte 2 des variables aux entrées d'adresse ou de commande. Par exemple  $z \grave{a} A_1$  et  $y \grave{a} A_0$ . On doit ensuite connecter convenablement les 4 entrées de données de façon à reproduire les différents termes de la fonction F.

- Pour le terme  $x \cdot y \cdot \overline{z}$  on doit relier l'entrée  $E_1$  dont l'adresse est 01 (z = 0, y = 1) à x.

- Pour le terme  $\overline{x} \cdot \overline{y} \cdot z$  on doit relier l'entrée  $E_2$  dont l'adresse est  $\mathbf{10} (z = 1, y = 0)$  à  $\overline{x}$ .

- Pour le terme  $z \cdot y$  on relie l'entrée  $E_3$  dont l'adresse est  $11 \ (z = 1, y = 1)$  au niveau logique 1.

- Toutes les autres entrées sont connectées au niveau logique  $\mathbf{0}$  (la masse) puisque  $\mathbf{F} = \mathbf{0}$  pour les valeurs de  $\mathbf{y}$  et  $\mathbf{z}$  correspondantes.

Année : 2022-2023

Ingénierie

#### b. Démultiplexeur :

Un démultiplexeur joue le rôle inverse du multiplexeur. Il permet de faire passer une entrée de donnée, dans l'une des sorties selon les valeurs des entrées de commandes. Il possède :

- une entrée unique d'information (donnée)

- *n* entrées de commandes (adresses).

- m sorties  $(m \le 2^n)$ .

Application pratique: Transformation série parallèle.

**Exemple 7 :** Démultiplexeur à N=2 entrées de commande

#### Remarque

La plupart des multiplexeurs/démultiplexeurs sont munis d'une entrée supplémentaire : entrée de validation permettant d'activer ou non le circuit. Lors de la désactivation, les sorties peuvent être placées soit à l'état inactif ("0") soit dans un état dit "haute impédance".

# **Biobibliographie:**

- [1] "Digital Logic and Computer Design" par M. Morris Mano.

- [2] "Conception des circuits logiques numériques" par M. Morris Mano.

- [3] "Circuit numériques : principes et pratique" par John M. Yarbrough.

# CHAPITRE 3: LOGIQUES SÉQUENTIELS.

"Chaque jour d'apprentissage est un pas vers une meilleure version de soi-même, un voyage qui ne cesse jamais d'enrichir notre âme."

# **CHAPITRE 3: SYSTEMES LOGIQUES SEQUENTIELS**

Année : 2022-2023

Ingénierie

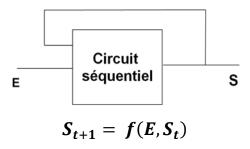

#### 3.1 Définition

Dans les circuits séquentiels, les signaux de sortie dépendent des entrées, mais aussi des états antérieurs : ils ont une mémoire du passé.

#### 3.2 Circuits asynchrones et synchrones

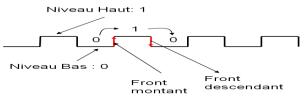

#### a. Horloge:

- Une horloge est une variable logique qui passe successivement de 0 à 1 et de 1 à 0 d'une façon périodique.

- L'horloge est notée par h, c ou ck (clock).

#### b. Circuits asynchrones et synchrones

Il existe deux types de circuits séquentiels

## - Systèmes asynchrones

Quand un circuit séquentiel n'a pas d'horloge comme variable d'entrée alors il est asynchrone. Dans ce cas, les sorties réagissent immédiatement aux variations des entrées, ce qui peut provoquer des états transitoires, des retards de durées différentes et des risques d'instabilité

#### - Systèmes Synchrones:

Le système mémorise l'état présent sur son entrée si et seulement si une horloge fournit un signal de synchronisation. Les circuits synchrones sont plus simples à synthétiser et à analyser.

#### 3.3 Bascules (Bistables):

Les bascules sont des circuits de bases de la logique séquentiel. Une bascule est une mémoire unitaire (1 bit) ayant 2 états :  $\mathbf{Q}$  et  $\overline{\mathbf{Q}}$ .

Année : 2022-2023

Ingénierie

Il existe plusieurs types de bascules : RS, RST, D, JK.

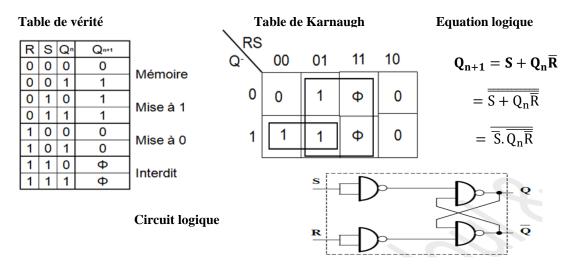

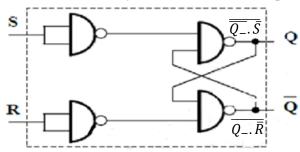

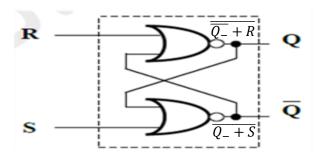

## 3.3.1 La bascule RS asynchrone

Entrée/sorties

- 2 entrées : **R et S**

- 2 sorties  $\mathbf{Qet} \ \overline{\mathbf{Q}}$  qui correspond à l'état stocké et son inverse

Principe : la valeur de Q à t+1 dépend de R( reset ) et S(set) et de la valeur de Q à t

- S = 1 et R = 0 : Q mis à 1

- S = 0 et R = 1 : Q mis à 0

- L'état R = S = 0 (mode mémoire) maintient l'état de la sortie.

- L'état R = S = 1 (mode interdit) est interdit car il conduit à mettre simultanément la sortie à 1 et à 0.

| T | able | e de fon       | ctionnement | $\mathbf{S}\mathbf{y}$ | mbole                 |

|---|------|----------------|-------------|------------------------|-----------------------|

| R | S    | Q <sup>+</sup> |             | S                      | 0                     |

| 0 | 0    | Q-             | Mémoire     | ľ                      | ~                     |

| 0 | 1    | 1              | Mise à 1    |                        |                       |

| 1 | 0    | 0              | Mise à 0    | Ь                      | $\overline{\bigcirc}$ |

| 1 | 1    | Ф              | Interdit    | 11                     | <u> </u>              |

**Exemple1 :** Réalisation de la bascule RS asynchrone à l'aide des portes Nand.

- Cette bascule RS est prioritaire au 1 car, pour la combinaison R=S=1, la sortie Q est mise à 1 (les Φ ayant été fixés à 1 pour la simplification de Q).

**Exemple1**: Réalisation de la bascule RS asynchrone à l'aide des portes Nor.

#### Table de vérité Table de Karnaugh Equation logique R S Q Q<sub>n+1</sub> RS 0 0 0 0 11 10 00 01 $\mathbf{Q}_{n+1} = \overline{\mathbf{R}}.\left(\mathbf{Q}_n + \mathbf{S}\right)$ Mémoire 0 1 0 1 0 1 1 1 0 0 Φ $=\overline{\overline{\overline{R}.\left(Q_{n}+S\right)}}$ Mise à 1 1 1 1 0 0 0 1 1 Φ 0 Mise à 0 $=\overline{\overline{R+(\overline{Q_n+S})}}$ 0 1 0 1 0 Φ Interdit 1 1 Φ R Circuit logique

Année: 2022-2023

Ingénierie

Cette bascule RS est <u>prioritaire au 0</u> car, pour la combinaison R=S=1, la sortie Q est mise à 0 (les  $\Phi$  ayant été fixés à 0 pour la simplification de Q).

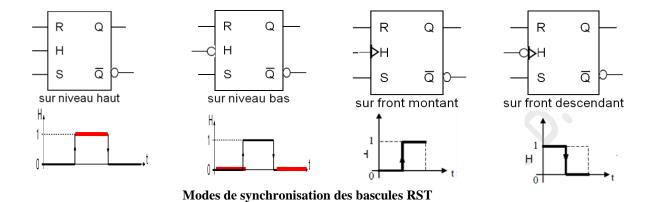

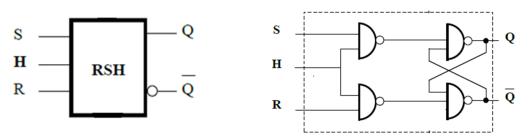

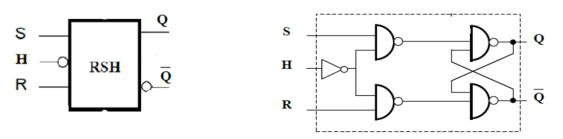

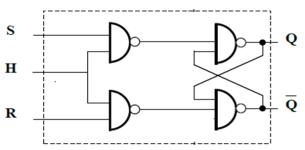

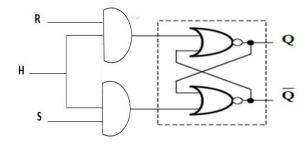

## 3.3.2 La bascule RS synchrone

Pour une bascule RS synchrone l'enclenchement et le déclenchement ne sont donc autorisés qu'à la présence du signal d'horloge H.

La bascule RS synchrone fonctionne en fonction de l'horloge selon 4 Modes :

- Niveau haut : la bascule n'est active que si l'horloge est à 1

- Niveau bas: la bascule n'est active que si l'horloge est à 0

- Sur le front montant de l'horloge

- Sur le front descendant de l'horloge

Exemple 3: La bascule RST synchronisée par le niveau haut de l'horloge

Année : 2022-2023

Ingénierie

Exemple 4: La bascule RST synchronisée par le niveau bas de l'horloge

**Remarque** La synchronisation sur niveau a beaucoup d'inconvénients : la bascule est sensible aux entrées pendant toute la durée de l'état de l'horloge pour niveau haut (ou 0 pour le niveau bas). Si, pendant que H =1 (ou H=0), des parasites apparaissent sur les entrées S et R, ils peuvent entrainer des changements d'état imprévus sur la sortie Q.

Afin de minimiser au maximum la durée de cet état sensible, on s'arrange pour que la bascule reste dans son état mémoire sauf pendant un bref instant, juste au moment où l'entrée passe de 0 à 1 (ou de 1 à 0). La bascule est dite synchronisée sur front.

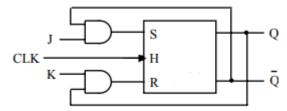

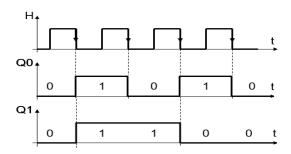

#### 3.3.3 Bascule J-K

La bascule JK (variante de RS) est une bascule synchrone (le plus souvent sur front) qui possède une entrée J de mise à 1 (S), une entrée K de mise à 0 (R), une entrée d'horloge H, une sortie Q et une sortie complément de Q.

La différence entre la bascule JK et la bascule RS réside dans le fait qu'il n'y a plus l'état indécis. La combinaison J=1 et K=1 est utilisée pour faire basculer la sortie, dans ce cas elle passe à l'état complémentaire :  $Q^+ = \overline{Q^-}$  (*basculement*).

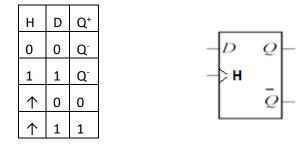

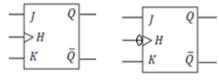

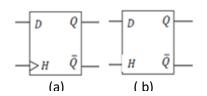

#### 3.3.4 Bascule D

La bascule D est une bascule synchrone qui possède une entrée de donnée D (Data), une entrée d'horloge H, une sortie Q et une sortie complément de Q.

Le signal de synchronisation est actif:

- Soit sur un niveau (haut ou bas) de l'horloge (bascule D latch)

- Soit sur un front (montant ou descendant) de l'horloge (bascule D edge triggered)

Exemple 5 : Bascule *D latch* synchronisée par le niveau haut :

| Н | D | Q⁺             |

|---|---|----------------|

| 0 | 0 | Q <sup>-</sup> |

| 0 | 1 | Q <sup>-</sup> |

| 1 | 0 | 0              |

| 1 | 1 | 1              |

La sortie recopie l'entrée sur le niveau haut d'horloge  $Q^+ = D$ . Sur le niveau bas, la sortie est mémorisée

Année: 2022-2023

Ingénierie

**Exemple 6 :** Bascule *D* edge triggered synchronisée par le front montant :

La sortie recopie l'entrée sur un front montant d'horloge sinon elle ne change pas d'état (maintien de l'état, mémorisation).

# **Biobibliographie:**

- [1] "Digital Logic and Computer Design" par M. Morris Mano.[2] "Digital Systems: Principles and Applications" par Ronald J. Tocci.

# Fiche TD 1 : Logique combinatoire et Logique Séquentielle.

Année: 2022-2023

Ingénierie

Partie 1 : Rappel des principes fondamentaux de l'algèbre de Boole

| Propriétés de l'algèbre de Boole   | Théorèmes de l'algèbre de Boole                                                     |

|------------------------------------|-------------------------------------------------------------------------------------|

| La commutativité: A. B=B.A         | Théorème d'involution : $\overline{\overline{A}}$ = A                               |

| A+B=B+A                            | $\overline{\overline{\overline{\overline{A}}}} = \overline{\overline{A}}$           |

| L'associativité : (A.B).C=A. (B.C) | Théorème d'inclusion : A.B+A.B=A                                                    |

| (A+B)+C=A+(B+C)                    | $(A+B).(A+\overline{B})=A$                                                          |

| La priorité: A+B.C=A+ (B.C)        | Théorème d'allégement : A.(A+B)=A.B                                                 |

|                                    | $A+(\overline{A}.B)=A+B$                                                            |

| La distributivité :                | Théorème d'absorption : A.(A+B) =A                                                  |

| A.(B+C) = (A.B) + (A.C) = A. B+A.C | A+(A.B)=A                                                                           |

| A+(B.C) = (A+B).(A+C)              |                                                                                     |

| Les éléments neutres : A.1= A      | Théorème de Morgan: $\overline{A} \cdot \overline{B} = \overline{A} + \overline{B}$ |

| A+0= A                             | $\overline{A + B} = \overline{A}.\overline{B}$                                      |

| Les éléments absorbants : A.0= 0   |                                                                                     |

| A+1=1                              |                                                                                     |

| La complémentarité : A.A=0         |                                                                                     |

| $\overline{A}+A=1$                 |                                                                                     |

| L'idempotence : A. A=A             |                                                                                     |

| A+A=A                              |                                                                                     |

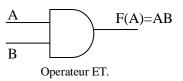

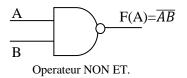

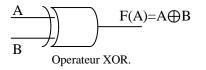

|                                                                                                                                                                                                                                  | Operateurs élémentair                                                                                                                                                                                      | es de l'algèbre de Boole                  | I                                                                                                                |                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| NON $ \begin{array}{c cc} Entrée & Sortie \\ \hline A & F = \overline{\overline{A}} \\ \hline 0 & 1 \\ \hline 1 & 0 \end{array} $                                                                                                | OU (OR)  Les entrées   Sortie   A   B   F=A+B   0   0   0   0   1   1   1   0   1   1   1   1                                                                                                              | ET (AND)    Les entrées   Sortie     A    | NON ET (NA Les entrées  A B  0 0  0 1  1 0  1 1                                                                  | ND) Sortie $F = \overline{A \cdot B}$ $1$ $1$ $1$ $0$ |

| NON OU (NOR)           Les entrées         Sortie           A         B         F=\overline{A+B}           0         0         1           0         1         0           1         0         0           1         1         0 | XOR : $F(A,B) = A \oplus B = (A+B)(\bar{A} + \bar{B})$ Les entrées       Sortice         A       B $F = A$ 0       0       0         0       1       1         1       0       1         1       1       0 | $(A+\overline{B})(\overline{A}+B)$ Les er | $A \otimes B = $ $A \otimes B = $ $B \qquad F = A \otimes I$ $0 \qquad 1$ $1 \qquad 0$ $0 \qquad 0$ $1 \qquad 1$ | $A\overline{B}$ + AB =                                |

#### Représentation symbolique des opérateurs logique

$$\underbrace{\frac{A}{B}}_{Operateur\ OU.} F(A) = A + B$$

$$\begin{array}{c}

\underline{A} \\

\underline{B} \\

\underline{Operateur NON OU.} \\

0

\end{array}$$

$$\begin{array}{c}

A \\

\hline

B

\end{array}$$

Operateur Identité.

Année : 2022-2023

Ingénierie

#### **Exercice 1:**

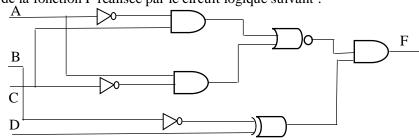

a. Donner le circuit logique des fonctions suivantes:

$$F(A, B, C, D) = \overline{(A + B). \overline{(B + \overline{C} + D)}. A}$$

$$F(A,B,C) = \overline{(AB)}.(C \odot B) + A \overline{B}C$$

b. Dresser la table de vérité de la fonction suivante:

$$F(A, B, C) = \overline{(A.B)}.(C + B) + A\overline{B}C$$

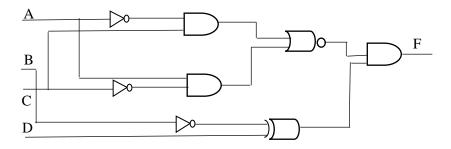

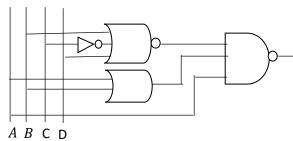

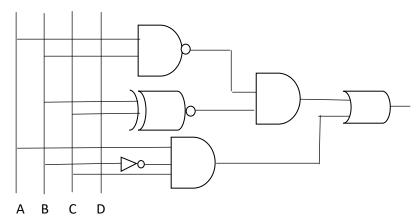

c. Donner l'équation de la fonction F réalisée par le circuit logique suivant :

Ecole Supérieure en Génie Electrique et Energétique d'Oran Département des Classes préparatoires

#### **Exercice 2:**

A partir de la table de vérité ci-dessous :

| Α | В | C | F(A,B,C) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | 1        |

| 0 | 1 | 1 | 0        |

| 1 | 0 | 0 | 1        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | 1        |

| 1 | 1 | 1 | 0        |

a. Etablir l'équation logique de la sortie F en fonction des entrées sous sa première forme canonique.

Année: 2022-2023

Ingénierie

- b. Etablir l'équation logique de la sortie F en fonction des entrées sous sa deuxième forme canonique.

- c. En utilisant les propriétés de l'algèbre de Boole, simplifier la première forme de F puis schématiser son logigramme à l'aide des portes logiques de base.

#### **Exercice 3:**

a. Donner la table de Karnaugh qui correspond à la table de vérité ci-dessous, puis utiliser la (TK) pour simplifier la fonction F.

| A | В | С | F(A,B,C) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | 1        |

| 0 | 1 | 1 | 0        |

| 1 | 0 | 0 | 1        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | 1        |

| 1 | 1 | 1 | 0        |

b. Pour chacune des fonctions logiques suivantes, établir la (TK), puis simplifier l'expression.

$$F(A, B, C) = A\overline{C} + A\overline{B} + ABC + \overline{A}\overline{B}\overline{C}$$

$$F(A, B, C, D) = \overline{A}B\overline{C} + \overline{A}\overline{C}D + \overline{A}\overline{B}\overline{D} + AC + BC\overline{D}$$

$$F(A, B, C, D) = (A + B).(B + \overline{C}).(A + D)$$

Partie 2 : Logique combinatoire

### **Exercice 1**

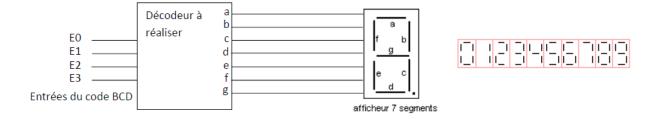

**a.** Dresser la table de vérité du transcodeur *BCD*/ 7 segments. Les sorties seront considérées indéterminées (X) pour les combinaisons d'entrée non valides. Elles valent 1 quand le segment doit être allumé

Année: 2022-2023

Ingénierie

- **b.** A l'aide du tableau de Karnaugh déterminer les expressions simplifiées des sorties a et d.

- **c.** Proposer un logigramme pour la sortie a avec un minimum de portes logiques.

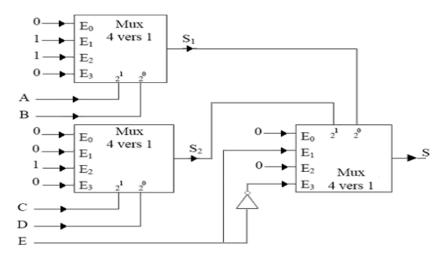

#### Exercice 2:

- a. Réaliser un multiplexeur à 3 entées de commande à l'aide de 2 multiplexeurs à 2 entrées d'adresse.

- b. Soit le schéma ci-dessous : Donnez l'équation de S en fonction de: A, B, C, D, et E.

- **c.** A l'aide d'un multiplexeur à 3 entrées d'adresses, réaliser la fonction **d** de l'exercice précédent (transcodeur **BCD/7** segments)

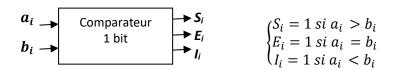

#### **Exercice 3:**

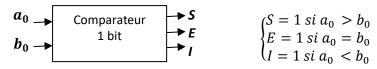

La figure suivante représente un comparateur de deux nombres binaires  $a_i$  et  $b_i$  à 1 bit

- a. Effectuer la synthèse de ce circuit logique.

- **b.** On prend deux nombres de deux bits chacun en entrée, soit  $a_1a_0$  et  $b_1b_0$ , déduire à partir de a les équations des trois sorties de ce comparateur 2 bits.

#### Partie 3 : logique séquentielle

#### **Exercice 1**

- **a.** Rappeler la table de vérité d'une bascule RS.

- **b.** Proposer un circuit logique d'une bascule RS asynchrone(vérifier à partir du circuit les deux fonction Q et  $\overline{Q}$  a l'instant t+1), ensuite synchrone sur niveau haut de l'horloge en utilisant des portes NAND.

- c. Proposer un circuit logique d'une bascule RS asynchrone(vérifier à partir du circuit les deux fonction Qet  $\overline{Q}$  a l'instant t+1), ensuite synchrone sur niveau haut de l'horloge en utilisant des portes NOR.

- **d.** Rappeler la table de vérité d'une bascule JK, et proposer ensuite une réalisation de JK à l'aide d'une bascule SR.

#### Exercice 2

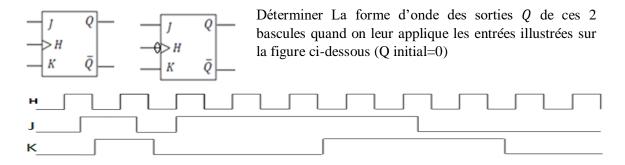

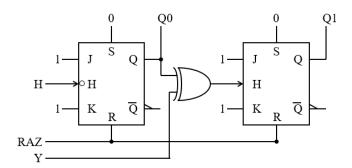

Soient les 2 bascules JK suivantes :

Année : 2022-2023

Ingénierie

#### **Exercice 3**

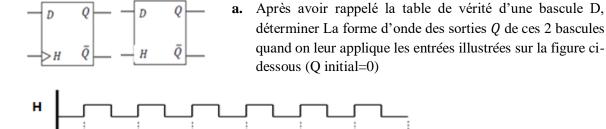

Soient les 2 bascules D suivantes :

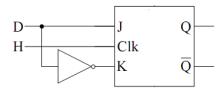

b. Comment peut-on réaliser une bascule D à partir d'une bascule JK

# Solution Fiche TD 1: Logique combinatoire et Logique Séquentielle.

Année : 2022-2023

Ingénierie

#### Partie 1:

#### **Exercice 1:**

a. Donner le circuit logique des fonctions suivantes:

$$F(A, B, C, D) = \overline{(A + B). \overline{(B + \overline{C} + D)}. A}$$

$$F(A,B,C) = \overline{(AB)}.(C \odot B) + A \overline{B}C$$

b. Dresser la table de vérité de la fonction suivante:

$$F(A, B, C) = \overline{(A.B)}.(C + B) + A\overline{B}C$$

| Α | В | C | F(A,B,C) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | 1        |

| 0 | 1 | 1 | 1        |

| 1 | 0 | 0 | 0        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | 0        |

| 1 | 1 | 1 | 0        |

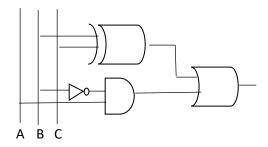

c. Donner l'équation de la fonction F réalisée par le circuit logique suivant :

Année: 2022-2023

Ingénierie

$$F(A, B, C, D) = (\overline{AC + A\overline{C}})(\overline{B} \oplus D) = (\overline{A \oplus C})(\overline{B} \oplus D) = (A \otimes C)(\overline{B} \oplus D)$$

#### Exercice 2:

A partir de la table de vérité ci-dessous :

| Α | В | С | F(A,B,C) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | 1        |

| 0 | 1 | 1 | 0        |

| 1 | 0 | 0 | 1        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | 1        |

| 1 | 1 | 1 | 0        |

- a. Etablir l'équation logique de la sortie F en fonction des entrées sous sa première forme canonique.  $F_1(A,B,C) = \bar{A}\bar{B}C + \bar{A}B\bar{C} + A\bar{B}\bar{C} + A\bar{B}\bar{C} + A\bar{B}\bar{C}$

- b. Etablir l'équation logique de la sortie F en fonction des entrées sous sa deuxième forme canonique.  $F_2(A,B,C)=(A+B+C)(A+\bar{B}+\bar{C})(\bar{A}+\bar{B}+\bar{C})$

- c. En utilisant les propriétés de l'algèbre de Boole, simplifier la première forme de F puis schématiser son logigramme à l'aide des portes logiques de base.

$$\begin{split} &F_{1}(A,B,C) = \bar{A}\bar{B}C + \bar{A}B\bar{C} + A\bar{B}\bar{C} + A\bar{B}C + AB\bar{C} \\ &= B\bar{C}(\bar{A} + A) + A\bar{B}(\bar{C} + C) + \bar{A}\bar{B}C \\ &= B\bar{C} + \bar{B}(A + \bar{A}C) = B\bar{C} + \bar{B}(A + C) = B\bar{C} + \bar{B}A + \bar{B}C = \bar{B}A + (B \oplus C) \end{split}$$

# Exercice 3:

c. Donner la table de Karnaugh qui correspond à la table de vérité ci-dessous, puis utiliser la (TK) pour simplifier la fonction F.

Année: 2022-2023

Ingénierie

| Α | В | С | F(A,B,C) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 1        |

| 0 | 1 | 0 | 1        |

| 0 | 1 | 1 | 0        |

| 1 | 0 | 0 | 1        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | 1        |

| 1 | 1 | 1 | 0        |

| C  | 0 | 1 |

|----|---|---|

| AB |   |   |

| 00 | 0 | 1 |

| 01 | 1 | 0 |

| 11 | 1 | 0 |

| 10 | 1 | 1 |

| ,  |   |   |

$$F(A,B,C) = B\bar{C} + \bar{B}A + \bar{B}C$$

d. Pour chacune des fonctions logiques suivantes, établir la (TK), puis simplifier l'expression.  $F(A,B,C) = A\overline{C} + A\overline{B} + ABC + \overline{A}\overline{B}\overline{C}$

| C  | 0 | 1 |

|----|---|---|

| AB |   |   |

| 00 | 1 | 0 |

| 01 | 0 | 0 |

| 11 | 1 | 1 |

| 10 | 1 | 1 |

$$F(A, B, C) = A + \bar{B}\bar{C}$$

$$F(A, B, C, D) = \overline{A}B\overline{C} + \overline{A}\overline{C}D + \overline{A}\overline{B}\overline{D} + AC + BC\overline{D}$$

| CD | 00 |   | 01 | 11 | 10 |

|----|----|---|----|----|----|

| AB | _  |   |    |    |    |

| 00 | ſ  | 1 | 1  | 0  | 1  |

|    |    |   |    |    |    |

| 01 |    | 1 | 1  |    | 1  |

| 11 | -  | 0 | 1  | 1  | 1  |

|    |    | Ü |    |    |    |

| 10 |    | 0 | 0  | 0  | 0  |

|    |    |   |    |    |    |

$$F(A, B, C, D) = \overline{AC} + \overline{AD} + BC + BD$$

$F(A, B, C, D) = (A + B).(B + \bar{C}).(A + D)$

| CD | 00 |   | 01 | 11 | 10 |

|----|----|---|----|----|----|

| AB | _  |   |    | 1  |    |

| 00 |    | 0 | 0  | 0  | 0  |

| 01 | _  | 0 | 1  | 1  | 0  |

| 11 |    | 1 | 1  | 1  | 1  |

| 10 |    |   | 1  | 0  | 0  |

Année: 2022-2023

Ingénierie

$$F(A, B, C, D) = (A + B) \cdot (B + \overline{C}) \cdot (A + D)$$

#### Partie 2:

#### **Exercice 1:**

**a.** Dresser la table de vérité du transcodeur *BCD*/ 7 segments. Les sorties seront considérées indéterminées (X) pour les combinaisons d'entrée non valides. Elles valent 1 quand le segment doit être allumé.

| $\mathbf{E_0}$ | $\mathbf{E_1}$ | $\mathbf{E_2}$ | $\mathbf{E}_3$ | a | b | c | d | e | f | g |

|----------------|----------------|----------------|----------------|---|---|---|---|---|---|---|

| 0              | 0              | 0              | 0              | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

| 0              | 0              | 0              | 1              | 0 | 1 | 1 | 0 | 0 | 0 | 0 |

| 0              | 0              | 1              | 0              | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 0              | 0              | 1              | 1              | 1 | 1 | 1 | 1 | 0 | 0 | 1 |

| 0              | 1              | 0              | 0              | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 0              | 1              | 0              | 1              | 1 | 0 | 1 | 1 | 0 | 1 | 1 |

| 0              | 1              | 1              | 0              | 1 | 0 | 1 | 1 | 1 | 1 | 1 |

| 0              | 1              | 1              | 1              | 1 | 1 | 1 | 0 | 0 | 0 | 0 |

| 1              | 0              | 0              | 0              | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1              | 0              | 0              | 1              | 1 | 1 | 1 | 1 | 0 | 1 | 1 |

| 1              | 0              | 1              | 0              | ф | ф | ф | ф | ф | ф | ф |

| 1              | 0              | 1              | 1              | ф | ф | ф | ф | ф | ф | ф |

| 1              | 1              | 0              | 0              | ф | ф | ф | ф | ф | ф | ф |

| 1              | 1              | 0              | 1              | ф | ф | ф | ф | ф | ф | ф |

| 1              | 1              | 1              | 0              | ф | ф | ф | ф | ф | ф | ф |

| 1              | 1              | 1              | 1              | ф | ф | ф | ф | ф | ф | ф |

**b.** A l'aide du tableau de Karnaugh déterminer les expressions simplifiées des sorties *a* et *d*.

| $E_2 E_3$ | 00 | 01 | 11 | 10                               |

|-----------|----|----|----|----------------------------------|

| $E_0 E_1$ |    |    |    |                                  |

| 00        | 1  | 0  | 1  | 1                                |

| 01        | 0  | 1  | 1  | 1                                |

| 11        | ф  | ф  | ф  | ф                                |

| 10        |    | 1  | ф  | $\left[ \overline{\Phi} \right]$ |

|           |    |    |    |                                  |

$$a = \underline{E_2} + E_0 + E_1 E_3 + \overline{E_1} \ \overline{E_3}$$

| $E_2 E_3$ | 00 | 01 | 11  | 10 |

|-----------|----|----|-----|----|

| $E_0 E_1$ |    |    |     |    |

| 00        | 1  | 0  | 1   |    |

| 01        | 0  |    | 0   | 1  |

| 11        | ф  | ф  | ф   | ф  |

| 10        | 1  | 1  | ф   | Φ  |

|           |    |    | l l |    |

Année: 2022-2023

Ingénierie

$$d = E_0 + E_2 \overline{E_3} + \overline{E_1} \ E_2 + \overline{E_1} \ \overline{E_3} + E_1 \overline{E_2} \ E_3$$

$d = \underline{E}_0 + \underline{E}_2 \overline{\underline{E}_3} + \overline{E}_1 \ \underline{E}_2 + \overline{E}_1 \ \overline{E}_3 + \underline{E}_1 \overline{E}_2 \ \underline{E}_3$  **c.** Proposer un logigramme pour la sortie *a* avec un minimum de portes logiques.

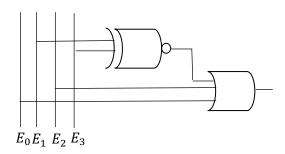

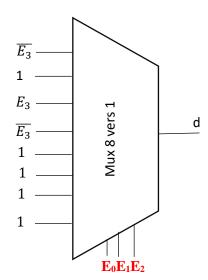

$$a=E_2+E_0+\ E_1E_3+\overline{E_1}\ \overline{E_3}=E_2+E_0+\ E_1\otimes E_3$$

## Exercice 2:

a. Réaliser un multiplexeur à 3 entées de commande à l'aide de 2 multiplexeurs à 2 entrées d'adresse. On utilise l'entrée de validation V (Strobe) comme troisième adresse  $a_2$ :

Quand

$$V=0$$

le  $MUX1$  est activé (MUX2 est desactivé) et  $Y=Y_1$  Quand  $V=1$  le  $MUX2$  est activé (MUX1 est desactivé) et  $Y=Y_2$

| a <sub>2</sub> =V | a <sub>1</sub> | <b>a</b> <sub>0</sub> | Y                     |

|-------------------|----------------|-----------------------|-----------------------|

| 0                 | 0              | 0                     | e <sub>0</sub>        |

| 0                 | 0              | 1                     | e <sub>1</sub>        |

| 0                 | 1              | 0                     | e <sub>2</sub>        |

| 0                 | 1              | 1                     | e <sub>3</sub>        |

| 1                 | 0              | 0                     | e <sub>4</sub>        |

| 1                 | 0              | 1                     | <b>e</b> <sub>5</sub> |

| 1                 | 1              | 0                     | e <sub>6</sub>        |

| 1                 | 1              | 1                     | <b>e</b> <sub>7</sub> |

b. Soit le schéma ci-contre : Donnez l'équation de S en fonction de A, B, C, D, et E .

$$S_1 = \overline{A}.B + A\overline{B} = A \bigoplus B$$

$$S_2 = C\overline{D}$$

$$S = \overline{S_2}S_1.E + S_2S_1\overline{E} = S_1(S_2 \oplus E) = A \oplus B(C\overline{D} \oplus E)$$

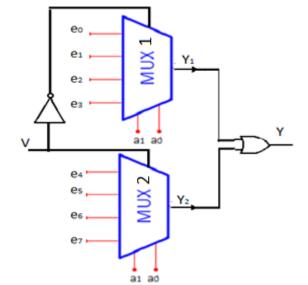

**c.** A l'aide d'un multiplexeur à 3 entrées d'adresses, réaliser la fonction *d* de **l'exercice 1 partie 2** (transcodeur *BCD*/ 7 segments)

Année: 2022-2023

Ingénierie

c.1) Table de vérité:

| $\mathbf{E_0}$ | $\mathbf{E_1}$ | $\mathbf{E_2}$ | $\mathbf{E}_3$ | d |

|----------------|----------------|----------------|----------------|---|

| 0              | 0              | 0              | 0              | 1 |

| 0              | 0              | 0              | 1              | 0 |

| 0              | 0              | 1              | 0              | 1 |

| 0              | 0              | 1              | 1              | 1 |

| 0              | 1              | 0              | 0              | 0 |

| 0              | 1              | 0              | 1              | 1 |

| 0              | 1              | 1              | 0              | 1 |

| 0              | 1              | 1              | 1              | 0 |

| 1              | 0              | 0              | 0              | 1 |

| 1              | 0              | 0              | 1              | 1 |

| 1              | 0              | 1              | 0              | ф |

| 1              | 0              | 1              | 1              | ф |

| 1              | 1              | 0              | 0              | ф |

| 1              | 1              | 0              | 1              | ф |

| 1              | 1              | 1              | 0              | ф |

| 1              | 1              | 1              | 1              | ф |

c.2) On prend  $E_0E_1E_2$  (l'ordre est important) comme entées d'adresse et  $E_3$  comme entrée de donnée, puis en utilisant la table de vérité on compare l'entrée  $E_3$  avec la sortie d, et on obtient :

Les cas indéterminés sont considérés comme des 1 au moment de la simplification, donc on les met a 1 à l'entrée du Multiplexeur.

Ecole Supérieure en Génie Electrique et Energétique d'Oran Département des Classes préparatoires

#### **Exercice 3:**

La figure suivante représente un comparateur de deux nombres binaires  $a_i$  et  $b_i$  à 1 bit

Année: 2022-2023

Ingénierie

- a. Effectuer la synthèse de ce circuit logique.

- a.1) les entrées : a<sub>0</sub> b<sub>0</sub>, les sorties S, E, I

- a.2) Table de vérité:

| $a_0$ | $b_0$ | S | Е | I |

|-------|-------|---|---|---|

| 0     | 0     | 0 | 1 | 0 |

| 0     | 1     | 0 | 0 | 1 |

| 1     | 0     | 1 | 0 | 0 |

| 1     | 1     | 0 | 1 | 0 |

a.3) Fonction logique :

$$S = a_0 \overline{b_0}$$

$E = \overline{a_0} \overline{b_0} + a_0 b_0 = a_0 \otimes b_0$   $I = \overline{a_0} b_0$

a.4) Logigramme:

b. On prend deux nombres de deux bits chacun en entrée, soit  $a_1a_0$  et  $b_1b_0$  Donner les équations des trois sorties de ce comparateur 2 bits.

$$\begin{array}{l} a_{1}a_{0}=b_{01}b_{1}\,signifie:\,a_{1}=b_{1}\,et\,a_{0}=b_{0}\,d'ou\,E=(a_{1}\otimes\,b_{1})(a_{0}\otimes\,b_{0})\\ a_{1}a_{0}< b_{1}b_{0}\,signifie:\,a_{1}< b_{1}\,ou\,(a_{1}=b_{1}\,et\,a_{0}< b_{0})\,\,d'ou\,I=\overline{a_{1}}b_{1}+((a_{1}\otimes\,b_{1})\overline{a_{0}}b_{0})\\ a_{1}a_{0}> b_{1}b_{0}\,signifie:\,a_{1}> b_{1}\,ou\,(a_{1}=b_{1}\,et\,a_{0}> b_{0})\,\,d'ou\,S=\\ &=a_{1}\overline{b_{1}}+((a_{1}\otimes\,b_{1})a_{0}\overline{b_{0}}) \end{array}$$

#### Partie 3:

#### Exercice 1:

a. Rappeler la table de vérité d'une bascule RS.

| R | S | Q. | $Q_{+}$ |

|---|---|----|---------|

| 0 | 0 | 0  | 0       |

| 0 | 0 | 1  | 0       |

| 0 | 1 | 0  | 1       |

| 0 | 1 | 1  | 1       |

| 1 | 0 | 0  | 0       |

| 1 | 0 | 1  | 0       |

| 1 | 1 | 0  | ф       |

| 1 | 1 | 1  | ф       |

b. Proposer un circuit logique d'une bascule RS asynchrone(vérifier à partir du circuit les deux fonction Q et  $\overline{Q}$  a l'instant t+1), ensuite synchrone sur niveau haut de l'horloge en utilisant des portes NAND.

Année: 2022-2023

Ingénierie

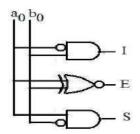

b.1) Circuit logique d'une bascule RS asynchrone en utilisant des portes NAND.

A partir du circuit on peut facilement déduire les équations  $Q_+$  et  $\overline{Q_+}$ :

$$Q_{+} = \overline{\overline{S}.\overline{Q_{-}.\overline{R}}}$$

(Fonction vérifiée)

$\overline{Q_+} = \overline{\overline{\overline{Q_-}.\overline{S}}.\overline{R}}$  À vérifier avec la fonction obtenue à partir de la table de vérité :  $\overline{Q_+} = \overline{S}.\overline{Q_-.\overline{R}}$

$$\overline{Q_{+}} = \overline{\overline{\overline{Q_{-}}.\overline{S}}.\overline{R}} = \overline{S}.\overline{Q_{-}} + R = \overline{\overline{\overline{S}}.\overline{Q_{-}} + R} = \overline{S}.\overline{Q_{-}.\overline{R}}$$

b.2) Circuit logique d'une bascule RS synchrone sur niveau haut de l'horloge en utilisant des portes NAND

- c. Proposer un circuit logique d'une bascule RS asynchrone(vérifier à partir du circuit les deux fonction Qet  $\overline{Q}$  a l'instant t+1), ensuite synchrone sur niveau haut de l'horloge en utilisant des portes NOR.

- c.1) Circuit logique d'une bascule RS asynchrone en utilisant des portes NOR

A partir du circuit on peut facilement déduire les équations  $Q_+$  et  $\overline{Q_+}$ :

$$Q_{+} = \overline{R + (\overline{Q_{-} + S})}$$

À vérifier avec la fonction obtenue à partir de la table de vérité :  $\overline{Q_+} = R + (\overline{Q_- + S})$

$$\overline{Q_{+}} = \overline{\overline{R + \overline{Q_{-}}} + S} = R + \overline{Q_{-}}.\overline{S} = \overline{R + \overline{Q_{-}}.\overline{S}} = R + (\overline{Q_{-}} + S)$$

c.2) Circuit logique d'une bascule RS synchrone sur niveau haut de l'horloge en utilisant des portes NOR

Année : 2022-2023

Ingénierie

- d. Rappeler la table de vérité d'une bascule JK, et proposer ensuite une réalisation de JK à l'aide d'une bascule SR.

- d.1) Rappeler la table de vérité d'une bascule JK

| J | K | Q. | $Q_{+}$ |

|---|---|----|---------|

| 0 | 0 | 0  | 0       |

| 0 | 0 | 1  | 0       |

| 0 | 1 | 0  | 1       |

| 0 | 1 | 1  | 1       |

| 1 | 0 | 0  | 0       |

| 1 | 0 | 1  | 0       |

| 1 | 1 | 0  | 1       |

| 1 | 1 | 1  | 0       |

d.2) Proposer ensuite une réalisation de JK à l'aide d'une bascule SR.

Le fonctionnement de la bascule JK à partir de SR est comme suit :

- 1. Si J = K = 0 Les entrées S et R sont à 0. La bascule RS garde l'état précédent des sorties  $Q_-$  et  $\overline{Q}_-$ .

- 2. Si J = 0 et K = 1 L'entrée S est bloquée à 0, tandis que l'entrée R varie selon la valeur de Q\_.

- Si  $Q_{-} = 0$ , l'entrée R =0 les sorties gardent les états précédents.

- Si  $Q_{-}=1$ , l'entrée R=1, la sortie  $Q_{+}$  est mise à 0.

Donc quel que soit la valeur de  $Q_{-}$ , la sortie  $Q_{+}$  est mise à 0 quand J=0 et K=1.

- 3. Si J = 1 et K = 0 L'entrée R est bloquée à 0, tandis que l'entrée J varie selon la valeur de  $\overline{Q}$ .

- Si  $\overline{Q}_{-} = 0$ , l'entrée S =0 les sorties gardent les états précédents ( $Q_{-} = 1$ ).

- Si  $\overline{\mathbf{Q}}_{-}$  =1, l'entrée S = 1, la sortie  $\mathbf{Q}_{+}$  est mise à 1.

Donc quel que soit la valeur de  $\overline{Q}_{-}$ , la sortie  $Q_{+}$  est mise à 1 quand J = 1 et K = 0.

- 4. Si J = K = 1 Dans ce cas les retours croisés des sorties  $Q_{-}$  et  $\overline{Q_{-}}$  donne lieu un état de basculement.

- Si  $(Q_- = 0 \text{ donc } \overline{Q_-} = 1)$ , Au top d'horloge  $Q_+ = 1$  et  $\overline{Q_+} = 0$ .

- Si  $(Q_- = 1 \text{ donc } \overline{Q_-} = 0)$ , Au top d'horloge  $Q_+ = 0$  et  $\overline{Q_+} = 1$ .

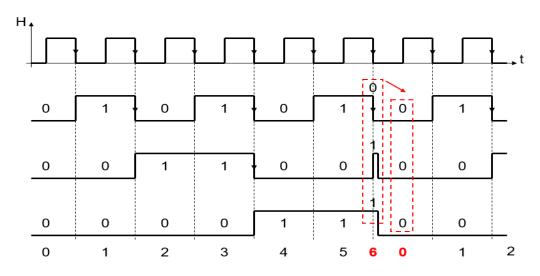

#### **Exercice 2:**

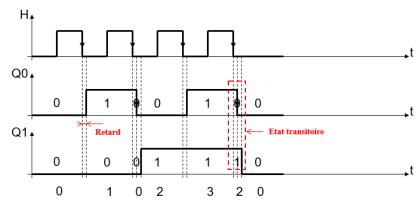

Soient les 2 bascules JK suivantes :

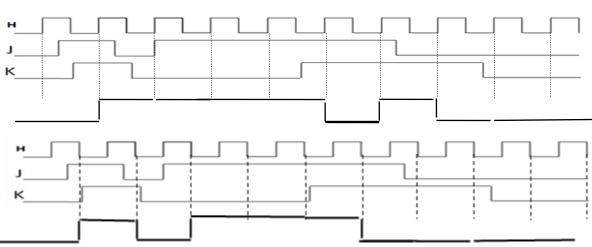

Déterminer La forme d'onde des sorties Q de ces 2 bascules quand on leur applique les entrées illustrées sur la figure cidessous (Q initial=0)

Année: 2022-2023

Ingénierie

#### Exercice 3:

Soient les 2 bascules D suivantes :

a. Après avoir rappelé la table de vérité d'une bascule D, déterminer La forme d'onde des sorties Q de ces 2 bascules quand on leur applique les entrées illustrées sur la figure cidessous (Q initial=0)

H Qa Qb

c. On peut réaliser une bascule D à partir d'une bascule JK en envoyant une donnée D sur l'entrée J et son inverse sur l'entrée K

Année: 2022-2023

Ingénierie

- 1. Si D=1, l'entrée J=1 et l'entrée K=0, au Top d'horloge  $Q_+$  est mise à 1.

- 2. Si D=0, l'entrée J=0 et l'entrée K=1, au Top d'horloge  $Q_+$  est mise à 0.

# CHAPITRE 4: COURS COMPTEURS/DÉCOMPTEURS.

"Apprendre, c'est faire grandir en soi une soif insatiable de savoir, une quête qui n'a ni début ni fin."

# **CHAPITRE 4 : COURS COMPTEURS/DECOMPTEURS**

Année: 2022-2023

Module : Ingénierie

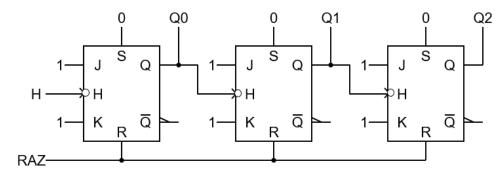

#### 4.1 Définitions :

- La réalisation d'un compteur/décompteur nécessite un ensemble de bascules (cellules élémentaires reliées) cadencées au rythme d'une horloge.

- Les bascules considérées pour la conception d'un compteur/décompteur peuvent être généralement de trois natures : bascule JK ( utiliser la propriété de basculement quand J = K = 1), bascule D (sortie  $\bar{Q}$  rebouclée sur l'entrée D) ou bascule T (mise à 1).

- Chaque bit de comptage est associé à l'état d'une bascule (commutant, ou pas), la concaténation de l'ensemble des états produira un mot binaire particulier qui définira l'état du compteur/décompteur. Le passage d'un état à l'autre du système (hors initialisation) est conditionné par les fronts actifs (montant ou descendant) du signal d'horloge.

- Un compteur modulo  $M = 2^n$  est un compteur dont la capacité de comptage est comprise entre [0, M 1] ([M 1, 0] pour un décompteur modulo  $M = 2^n$ ), sa réalisation nécessite par conséquent "n" bascules. Tout de même il est possible de concevoir un compteur/décompteur dont le cycle est modifiable, on parle à ce moment des compteurs/décompteurs programmables.

- Il existe principalement deux types de compteurs/décompteurs : les compteurs/décompteurs asynchrones et les compteurs/décompteurs synchrones. On note que les compteurs/décompteurs sont tous des circuits logiques synchrones, du moment où le passage d'un état à l'autre est conditionné par un top d'horloge. En effet, les deux termes synchrone et asynchrone ont un sens distinct que nous allons éclaircir dans la suite de ce cours.

# 4.2 Les compteurs/décompteurs Asynchrones :

Le principe de fonctionnement est celui de la mise au point d'une cascade de diviseurs de fréquence basculant sur fronts. On distingue ici deux catégories, celle des compteurs/décompteurs asynchrones binaires complet et celle des compteurs/décompteurs binaires asynchrones incomplets.

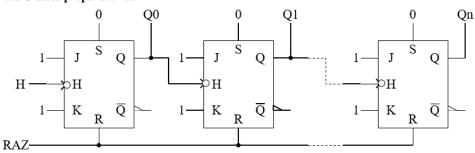

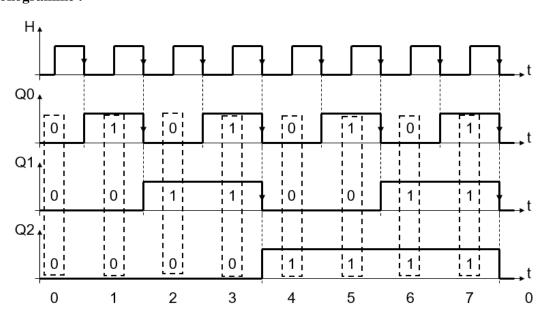

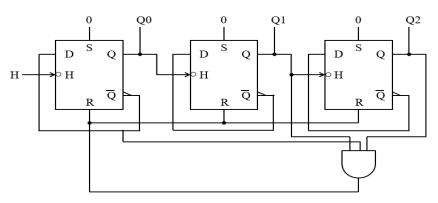

#### 4.2.1 Compteurs asynchrones modulo 2<sup>n</sup> (compteur binaire complet):

- Les bascules JK fonctionnent toutes en mode basculement (J=K=1)

- La première bascule (poids le plus faible) prend comme  $3^{\text{eme}}$  entrée l'horloge qui l'active ; l'une de ces sorties (Q ou  $\overline{Q}$  selon le front d'activation de l'horloge) servira par la suite d'horloge à la bascule qui la succède et ce processus continue jusqu'à la  $n^{\text{ième}}$  bascule. (Voir figure 1).

Année: 2022-2023

Module : Ingénierie

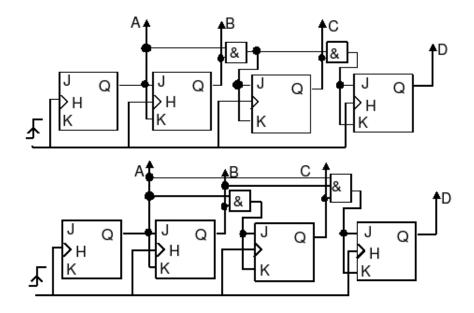

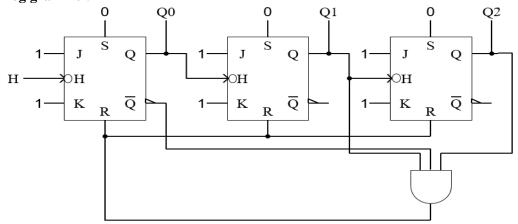

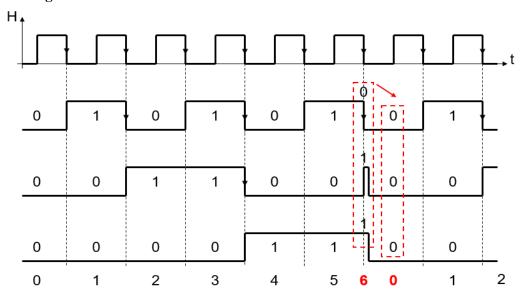

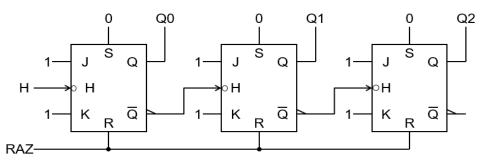

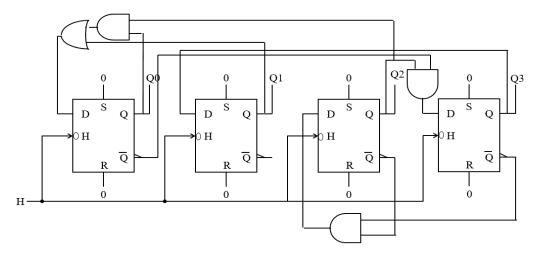

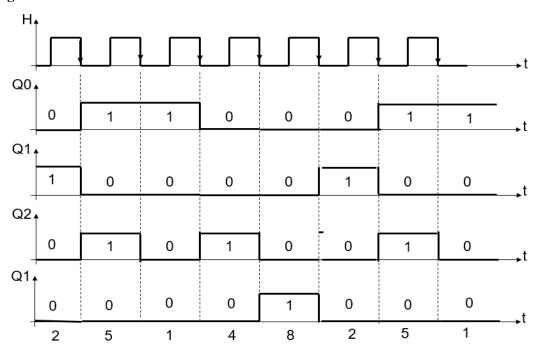

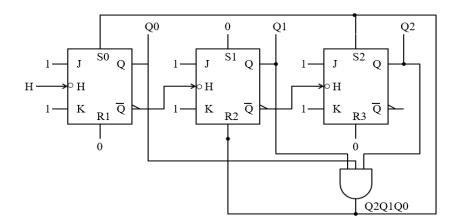

**Fig. 1**: Compteurs asynchrones modulo  $2^n$  à base de bascules JK actives sur front descendant.

**Exemple 1 :** synthétiser un compteur asynchrone modulo  $2^3 = 8$  active sur front descendant, et réalisé avec des bascules JK.

#### Table de vérité :

| R | Н             | $q_0$ | $q_1$ | $q_2$ | $Q_0$ | $Q_1$ | $Q_2$ |

|---|---------------|-------|-------|-------|-------|-------|-------|

| 1 | X             | X     | X     | X     | 0     | 0     | 0     |

| 0 | $\downarrow$  | 0     | 0     | 1     | 0     | 0     | 1     |

| 0 | $\downarrow$  | 0     | 1     | 0     | 0     | 1     | 0     |

| 0 | $\downarrow$  | 0     | 1     | 1     | 0     | 1     | 1     |

| 0 | $\rightarrow$ | 1     | 0     | 0     | 1     | 0     | 0     |

| 0 | $\downarrow$  | 1     | 0     | 1     | 1     | 0     | 1     |

| 0 | $\downarrow$  | 1     | 1     | 0     | 1     | 1     | 0     |

| 0 | $\downarrow$  | 0     | 0     | 1     | 1     | 1     | 1     |

## Logigramme:

## **Chronogramme:**

#### **N.B**:

- Pour un compteur à activation sur front montant, on connecte la sortie  $\overline{Q_n}$  à l'entrée de l'horloge  $H_{n+1}$ .

Année: 2022-2023

Module : Ingénierie

- Entrées de forçage asynchrones R: l'entrée CLEAR ou remise à zéro de l'état du compteur (active R=1 et inhibée R=0).

- Entrées de forçage asynchrones S: L'entrée PRESET ou remise à un de l'état du compteur (active S=1 et inhibée S=0).

#### **4.2.2** Compteurs binaires asynchrones incomplets:

On a régulièrement besoin d'un compteur modulo M (ou  $M \neq 2^n$ ), par exemple dans le cas où on veut dénombrer jusqu'à 12. Dans ce cas il est nécessaire de considérer un compteur asynchrone modulo  $2n \geq M$  et d'interrompre le cycle de comptage en provoquant une rétroaction sur les entrées CLEAR, au top d'horloge qui succède la valeur maximale à afficher (M-1).

**Exemple 2 :** synthétiser un compteur asynchrone modulo 6 (compte donc de :  $0 \rightarrow 5$ ) active sur front descendant, et réalisé à l'aide de bascules JK.

- Etape 1 : réaliser un compteur asynchrone binaire modulo 8

- Etape 2 : forcer la mise à 0 au moment que le compteur voudrait passer à la valeur 6.

#### Table de vérité :

| R | Н            | $q_2$ | $q_1$ | $q_0$ | $Q_2$               | $Q_1$ | $Q_0$ |

|---|--------------|-------|-------|-------|---------------------|-------|-------|

| 1 | X            | X     | X     | X     | 0                   | 0     | 0     |

| 0 | $\downarrow$ | 0     | 0     | 0     | 0                   | 0     | 1     |

| 0 | $\downarrow$ | 0     | 0     | 1     | 0                   | 1     | 0     |

| 0 | $\downarrow$ | 0     | 1     | 0     | 0                   | 1     | 1     |

| 0 | $\downarrow$ | 0     | 1     | 1     | 1                   | 0     | 0     |

| 0 | $\downarrow$ | 1     | 0     | 0     | 1                   | 0     | 1     |

| 1 | $\downarrow$ | 1     | 0     | 1     | 0                   | 0     | 0     |

|   |              |       |       |       | Forcer une mise à 0 |       |       |

#### Logigramme:

Chronogramme :

Année: 2022-2023

Module : Ingénierie

#### 4.2.3 Décompteurs asynchrones modulo 2<sup>n</sup> (décompteur binaire complet) :

Le même principe est appliqué pour le décompteur, la bascule du poids faible a comme  $3^{\rm eme}$  entrée l'horloge qui l'active; l'une de ces sorties (Q ou  $\overline{Q}$  selon le front d'activation de l'horloge) servira comme horloge à la bascule qui la succède et ce processus continue jusqu'à la  $n^{\rm ième}$  bascule. (Voir figure 2).

**Fig. 2**: Décompteurs asynchrones modulo  $2^n$  à base de bascules JK active sur front descendant.

#### **N.B**:

- Pour un décompteur à activation sur front montant, on connecte la sortie  $Q_i$  à l'entrée de l'horloge  $H_{i+1}$  (i allant de 0 à n-1).

**Exemple 2 :** synthétiser un décompteur asynchrone modulo  $2^3 = 8$  active sur front descendant et réalisé avec des bascules JK.

Ecole Supérieure en Génie Electrique et Energétique d'Oran Département des Classes préparatoires

#### Table de vérité :

| R | Н             | $q_0$ | $q_1$ | $q_2$ | $Q_0$ | $Q_1$ | $Q_2$ |

|---|---------------|-------|-------|-------|-------|-------|-------|

| 1 | X             | X     | X     | X     | 0     | 0     | 0     |

| 0 | $\rightarrow$ | 0     | 0     | 0     | 1     | 1     | 1     |

| 0 | $\rightarrow$ | 1     | 1     | 1     | 1     | 1     | 0     |

| 0 | $\rightarrow$ | 1     | 1     | 0     | 1     | 0     | 1     |

| 0 | $\rightarrow$ | 1     | 0     | 1     | 1     | 0     | 0     |

| 0 | $\rightarrow$ | 1     | 0     | 0     | 0     | 1     | 1     |

| 0 | $\rightarrow$ | 0     | 1     | 1     | 0     | 1     | 0     |

| 0 | $\rightarrow$ | 0     | 1     | 0     | 0     | 0     | 1     |

| 0 | $\downarrow$  | 0     | 0     | 1     | 0     | 0     | 0     |

## Logigramme:

Année: 2022-2023

Module : Ingénierie

#### **Chronogramme:**

## 4.2.4 Décompteurs binaires asynchrones incomplets :

Il est aussi possible de proposer une configuration pour un cycle de décomptage incomplet, il suffit de forcer le cycle de décomptage à s'initialiser à la valeur maximale souhaitée; en provoquant cette foisci une rétroaction sur les entrées CLEAR et /ou sur les entrées PRESET, au top d'horloge qui succède l'affichage de la valeur finale du cycle (0).

**Exemple 4:** synthétiser un décompteur asynchrone modulo 5  $(4\rightarrow 0)$  active sur front descendant et réalisé avec des bascules JK.

- Etape 1 : réaliser un décompteur asynchrone binaire modulo 8

- Etape 2 : forcer la mise à 4 ( $Q_0 = 0$  et  $Q_1 = 0$  et  $Q_2 = 1$ ) au moment où le compteur voudra passer à la valeur 7 ( $Q_0 = 1$  et  $Q_1 = 1$  et  $Q_2 = 1$ ). Pour cela on devrait faire appel aux deux touches PRESET ( $S_0 = 0$  et  $S_1 = 0$  et  $S_2 = 1$ ) et CLEAR ( $R_0 = 1$  et  $R_1 = 1$  et  $R_2 = 0$ ).

Année: 2022-2023

Module : Ingénierie

#### Table de vérité :

| Н            | $q_2$ | $q_1$ | $q_0$ | $Q_2$ | $Q_1$ | $Q_0$ |

|--------------|-------|-------|-------|-------|-------|-------|

| $\downarrow$ | 1     | 0     | 0     | 0     | 1     | 1     |

| $\downarrow$ | 0     | 1     | 1     | 0     | 1     | 0     |

| $\downarrow$ | 0     | 1     | 0     | 0     | 0     | 1     |

| $\downarrow$ | 0     | 0     | 1     | 0     | 0     | 0     |

| $\downarrow$ | 0     | 0     | 0     | 1     | 1     | 1     |

|              | 1     | 1     | 1     | 1     | 0     | 0     |

| X            | 1     | 1     | 0     | X     | X     | X     |

| X            | 1     | 0     | 1     | X     | X     | X     |

# Logigramme:

# **Chronogramme:**

Ecole Supérieure en Génie Electrique et Energétique d'Oran Département des Classes préparatoires

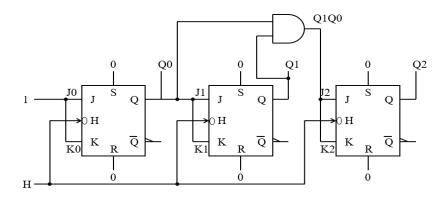

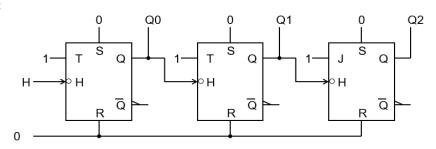

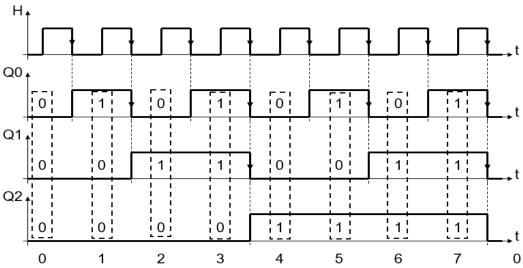

#### **4.2.5** Exercice 1:

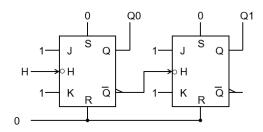

Proposer un logigramme qui synthétise en même temps un compteur et un décompteur asynchrone modulo 4 active sur front descendant en utilisant des bascules JK.

Année: 2022-2023

Module : Ingénierie

#### **Principe:**

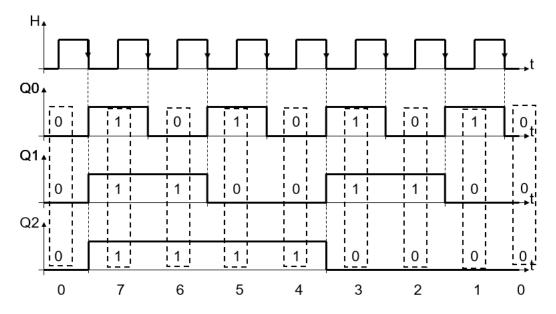

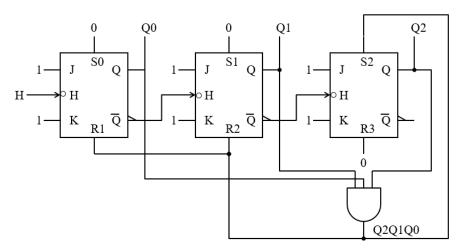

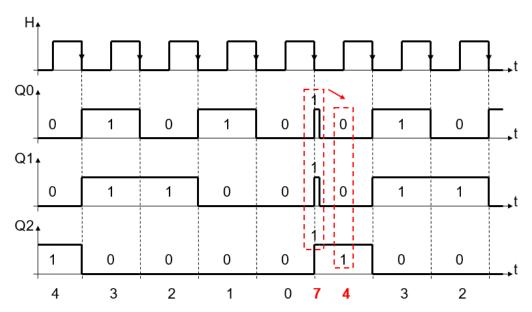

On doit prévoir une variable de choix Y qui permettra de trancher le sens du dénombrement (s'il s'agit d'un comptage ou un décomptage). Pour un compteur/décompteur active sur front descendant de l'horloge il est nécessaire de :

- conduire la sortie  $Q_n$  vers l'horloge  $H_{n+1}$ , si  $Y = 0 \rightarrow$  comptage;

- conduire la sortie  $Q_n$  complémentée vers l'horloge  $H_{n+1}$ , si  $Y=1 \rightarrow$  décomptage.

Pour se faire on utilise une porte ou exclusive :

#### Logigramme:

#### 4.2.6 Les avantages et limites des compteurs/décompteurs asynchrones :

Les compteurs/décompteurs asynchrones sont réputés par leur simplicité d'implémentation et sont généralement recommandés pour des configurations faisant intervenir un nombre limité (faible) de bascules. Au-delà d'un certain nombre de bascules les compteurs/décompteurs asynchrones engendrent des états transitoires non souhaités sur les sorties après chaque front de l'horloge ; et occasionnent une vitesse de fonctionnement très handicapante (limitée) (Voir figure 3). D'un autre côté, il arrive que l'on souhaite énumérer un cycle dont l'ordonnancement est aléatoire (différent du code binaire naturel). Dans ces cas de figures la solution réalisable est : "les compteurs/décompteurs synchrones".

Dans une configuration synchrone, le signal d'horloge est commun à toutes les bascules, en effet, les sorties des bascules changent d'état en même moment (après le front actif de l'horloge).

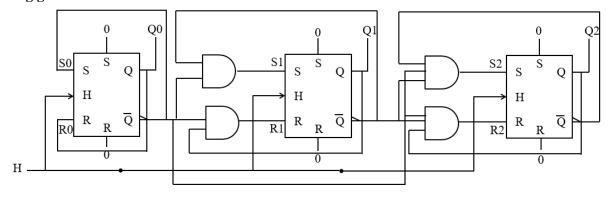

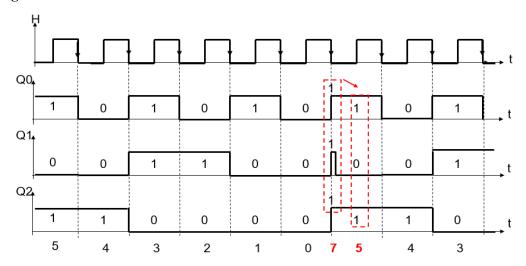

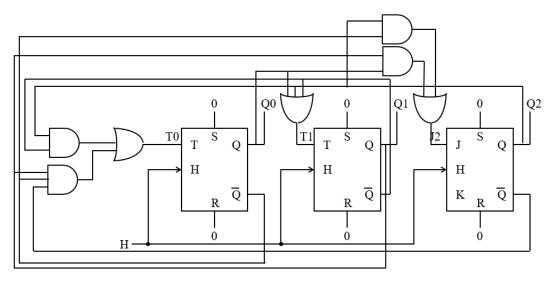

# 4.3 Synthèse d'un compteur/décompteur synchrone :

L'un des points fort d'une configuration synchrone est la possibilité de reproduire n'importe quel cycle de comptage, cela signifie qu'il est nécessaire d'effectuer une synthèse complète pour chaque cycle retenu.

Année: 2022-2023

Module : Ingénierie

Fig. 2 : états transitoires et retards engendrés par un compteur asynchrone.

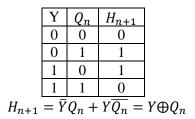

# 4.3.1 Table d'excitation d'une bascule :